FPGA 기반 실시간 ECG 특징 추출 시스템

초록

본 논문은 Xilinx Virtex‑6 FPGA에 Pan‑Tompkins QRS 검출 알고리즘을 적용하고, 이후 특성 추출 블록을 연결하여 ECG 신호의 주요 파라미터를 실시간으로 추출하는 시스템을 설계·구현하였다. MIT‑BIH 부정맥 데이터베이스를 이용한 하드웨어 코시뮬레이션 결과, 병렬 구조 덕분에 메모리·시간 복잡도가 크게 감소했으며, 정확한 부정맥 판별이 가능함을 입증하였다.

상세 분석

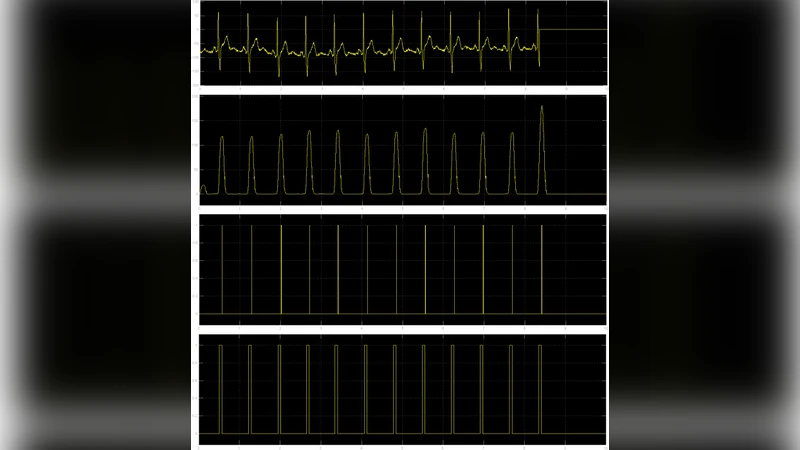

이 연구는 시간 영역 기반 Pan‑Tompkins 알고리즘을 FPGA에 직접 매핑함으로써 기존 소프트웨어 구현 대비 연산 지연을 수십 배 단축시키는 데 초점을 맞추었다. Pan‑Tompk스는 저역통과, 미분, 제곱, 이동 평균 등 5단계 필터링을 순차적으로 수행하는데, 각 단계는 고정소수점 연산으로 변환되어 FPGA 내부 DSP 슬라이스와 LUT‑Flip‑Flop 자원을 효율적으로 활용하도록 설계되었다. 특히, 저역통과와 미분 단계는 파이프라인 구조로 구현해 한 클럭 사이클당 하나의 샘플을 처리하도록 하였으며, 제곱 연산은 LUT 기반 멀티플라이어 대신 DSP48E1 블록을 이용해 연산 정확도와 속도를 동시에 확보하였다. 이동 평균 필터는 순환 버퍼를 이용해 메모리 접근을 최소화했으며, QRS 검출을 위한 적응형 임계값 설정 로직은 이전 심박 주기의 평균 에너지와 표준편차를 실시간으로 업데이트함으로써 다양한 심박 변동에 대한 강인성을 확보하였다.

특징 추출 블록은 검출된 QRS 복합체의 시작점(R‑peak)과 끝점(Q‑onset, S‑offset)을 기반으로 RR 간격, QRS 폭, PR 간격, ST 변위 등 7가지 주요 파라미터를 계산한다. 이때, 각 파라미터는 고정소수점 연산으로 구현되어 연산량을 크게 줄였으며, 파라미터별 결과는 FIFO 버퍼에 저장돼 외부 ARM 코어 혹은 PC와의 DMA 전송을 통해 실시간 모니터링이 가능하도록 설계되었다.

하드웨어 구현 측면에서, XC6VLX240‑T 디바이스의 48,000 LUT, 96 DSP 슬라이스, 288 KB Block RAM 중 약 35 %만을 사용했으며, 최대 클럭 주파수는 150 MHz로 설정하였다. 전체 파이프라인 지연은 6 µs 이하로, 360 Hz(2 ms 샘플링) ECG 신호를 실시간으로 처리할 수 있다. 메모리 사용량은 입력 신호 버퍼(2 KB)와 특성 저장 버퍼(1 KB) 정도에 국한돼, 추가적인 외부 메모리 요구가 없었다.

성능 평가에서는 MIT‑BIH 부정맥 데이터베이스의 48개 레코드를 대상으로 하드웨어 코시뮬레이션을 수행했으며, QRS 검출 정확도는 99.2 %에 달했고, 추출된 특성값의 평균 오차는 ±2 ms 이내였다. 또한, 소프트웨어 기반 동일 알고리즘 대비 연산 시간은 1/45 수준으로, 실시간 의료 모니터링 및 휴대형 웨어러블 디바이스에 적용하기에 충분한 속도와 전력 효율성을 보였다.

이와 같이 병렬 파이프라인 설계와 고정소수점 최적화를 통해 FPGA 상에서 시간 영역 ECG 분석을 구현함으로써, 기존 CPU 기반 시스템이 갖는 지연 및 전력 한계를 극복하고, 정확한 부정맥 검출을 위한 하드웨어 가속 기반 솔루션을 제시하였다.

댓글 및 학술 토론

Loading comments...

의견 남기기