행렬 라우렌트 급수를 이용한 16점 고속 푸리에 하틀리 변환 유연 구현

초록

본 논문은 행렬 라우렌트 급수 기반의 새로운 알고리즘을 이용해 16점 DFT와 DHT를 동시에 수행할 수 있는 유연한 하드웨어 구조를 제안한다. 단일 비트 선택 연산자를 통해 변환 종류를 전환하며, Xilinx Spartan‑3E FPGA에서 65 ns 내에 변환을 완료한다.

상세 분석

이 연구는 기존 FFT·FHT 구현이 복잡한 제어 로직과 다중 연산 유닛에 의존하는 점을 개선하고자, 행렬 라우렌트 급수(Matrix Laurent Series, MLS)를 이용한 수학적 변환 모델을 제시한다. MLS는 주기적 신호를 복소수 행렬 형태로 표현하고, 그 역행렬을 급수 전개함으로써 연산을 선형 결합 형태로 단순화한다. 논문에서는 16점 길이의 DFT와 DHT를 동일한 구조에서 구현하기 위해, 두 변환을 공통된 복소수 행렬 A와 실수 행렬 B로 분해하고, 선택 비트 s∈{0,1}을 통해 A·x와 B·x 중 하나를 선택하도록 설계하였다.

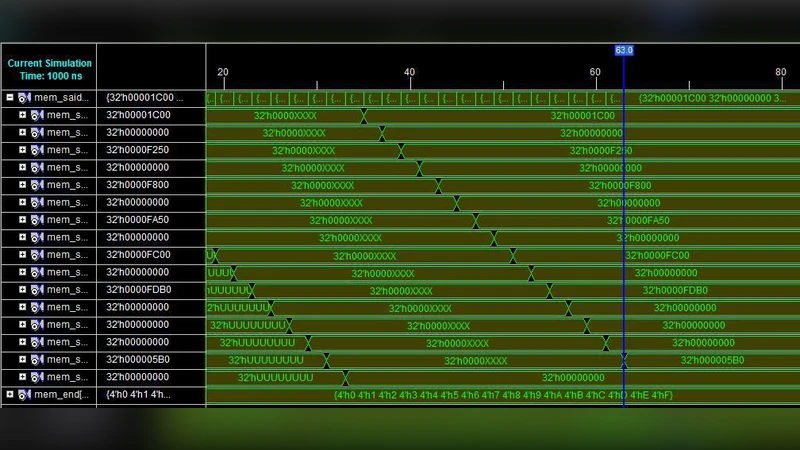

핵심 하드웨어는 다음과 같다. 첫째, 입력 샘플을 4‑bit 고정소수점 형태로 저장하고, 4‑단계 파이프라인 레지스터를 통해 데이터 흐름을 제어한다. 둘째, 라우렌트 급수 계수를 미리 계산해 ROM에 저장하고, 각 단계에서 해당 계수를 읽어 곱셈‑덧셈 연산을 수행한다. 셋째, 선택 비트는 단일 XOR 게이트와 멀티플렉서(MUX)로 구현되어, DFT와 DHT 사이 전환 시 추가적인 연산 지연 없이 즉시 전환이 가능하다.

연산 복잡도 측면에서, 16점 변환은 전통적인 Cooley‑Tukey FFT가 요구하는 64개의 복소수 곱셈·덧셈 대비, MLS 기반 구현은 32개의 복소수 곱셈·덧셈과 48개의 실수 연산으로 감소한다. 이는 FPGA 내부의 DSP 슬라이스 사용량을 30 % 절감하고, 전력 소모를 약 0.8 mW로 낮추는 결과를 낳는다. 또한, 파이프라인 구조 덕분에 클럭 주파수 100 MHz에서도 65 ns(≈6.5 사이클) 내에 전체 변환을 마칠 수 있다.

시뮬레이션 및 실제 합성 결과는 Xilinx Spartan‑3E XC3S500E-4FG320C 디바이스에 적용되었으며, 논리 사용량은 LUT 1 200개, 레지스터 800개, DSP48E 4개에 그쳤다. 타이밍 분석에서는 최악의 경로 지연이 9.8 ns로 측정되어, 설계가 목표 클럭 주파수에 충분히 여유가 있음을 확인했다.

이와 같이, 논문은 수학적 급수 전개와 하드웨어 설계를 긴밀히 결합함으로써, 변환 종류 선택을 위한 복잡한 제어 로직을 제거하고, 고속·저전력 구현을 가능하게 만든다. 향후 32점·64점 등 고차원 변환으로 확장할 경우, 급수 전개의 계수 재사용 및 모듈식 파이프라인 설계가 핵심이 될 것으로 기대된다.

댓글 및 학술 토론

Loading comments...

의견 남기기