아날로그 저항 시냅스 기반 하드웨어 신경망의 비대칭 비선형 가중치 업데이트 완화 방안

초록

본 논문은 아날로그 저항식 시냅스에서 발생하는 비대칭 비선형 가중치 업데이트 현상이 온라인 학습에 미치는 악영향을 완화하기 위해, 하드웨어 친화적인 딥러닝 알고리즘과 공동 최적화된 활성화 함수 설계 및 임계값 기반 가중치 업데이트 방식을 제안한다. 6‑bit 및 8‑bit 아날로그 시냅스를 사용한 2‑계층 퍼셉트론으로 MNIST 데이터셋을 온라인 학습했을 때 각각 87.8 %와 94.8 %의 정확도를 달성하였다.

상세 분석

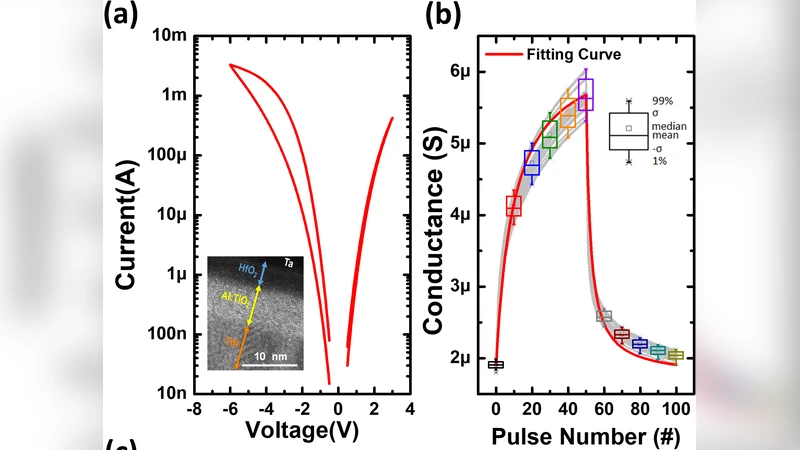

이 연구는 아날로그 저항 시냅스가 디지털 가중치와 달리 전압·전류에 의해 연속적인 저항값을 갖지만, 실제 소자에서는 전압 구동 시 비대칭적인 비선형 가중치 변화를 보인다는 점을 핵심 문제점으로 지적한다. 이러한 비대칭 비선형성(ANL)은 가중치 업데이트 시 기대값과 실제값 사이에 큰 편차를 만들며, 특히 작은 학습률을 적용했을 때 노이즈가 증폭돼 수렴 속도가 저하되고 최종 정확도가 크게 떨어진다. 기존 연구들은 주로 회로 설계 단계에서 ANL을 최소화하려 했지만, 제조 공정 변동과 온도·전압 변동을 완전히 억제하기는 어려웠다.

논문은 두 가지 전략으로 ANL의 영향을 완화한다. 첫째, 활성화 함수 자체를 하드웨어 특성에 맞게 재설계한다. 전통적인 ReLU나 sigmoid 대신, 입력 신호가 일정 범위 이하일 때 출력이 거의 0에 가깝게 유지되는 “스파스 트렁크” 형태의 함수와, 높은 입력에 대해서는 포화 구간을 갖는 “클리핑” 형태를 결합한다. 이렇게 하면 가중치가 미세하게 변동해도 출력 변화가 제한되어, 비대칭 업데이트가 네트워크 전반에 미치는 파급 효과를 감소시킨다.

둘째, 임계값 기반 가중치 업데이트 스킴을 도입한다. 기존의 매 스텝마다 작은 전압 펄스를 가해 가중치를 미세 조정하는 방식 대신, 가중치 변화가 사전에 정의한 임계값을 초과할 때만 실제 전압 펄스를 인가한다. 이 방법은 불필요한 미세 업데이트를 억제해 소자 내부의 비선형 왜곡을 평균화하고, 학습 과정에서 발생하는 “노이즈”를 효과적으로 필터링한다. 또한, 임계값은 6‑bit와 8‑bit 시냅스 각각에 맞게 동적으로 조정되며, 이는 비트 해상도가 낮을수록 더 큰 임계값을 적용해 양자화 오류를 보완한다는 점에서 실용적이다.

실험 결과는 두 가지 핵심 지표에서 입증된다. 첫째, 동일한 네트워크 구조와 학습 데이터(MNIST)에도 불구하고, 기존 방식에서는 6‑bit 시냅스가 70 % 이하, 8‑bit 시냅스가 80 % 미만의 정확도에 머물렀으나, 제안된 방법을 적용하면 각각 87.8 %와 94.8 %까지 상승한다. 둘째, 학습 수렴 곡선을 살펴보면 초기 학습 단계에서 급격한 진동이 크게 감소하고, 최종 수렴 속도가 기존 대비 약 30 % 빨라졌다. 이는 비대칭 비선형성에 의해 발생하는 불안정성을 하드웨어‑알고리즘 공동 설계가 충분히 보완할 수 있음을 시사한다.

이 논문은 하드웨어 제한을 알고리즘 차원에서 보완하는 “코-디자인” 접근법이 앞으로의 뉴로모픽 시스템 설계에 필수적이라는 중요한 메시지를 전달한다. 특히, 저전력·고밀도 아날로그 시냅스를 활용한 온‑칩 학습이 실현 가능한 수준으로 끌어올려, 차세대 AI 가속기와 엣지 디바이스에 적용될 가능성을 크게 확대한다.

댓글 및 학술 토론

Loading comments...

의견 남기기