표준 CMOS로 구현하는 초소형 메모리스터 에뮬레이터와 그 응용

초록

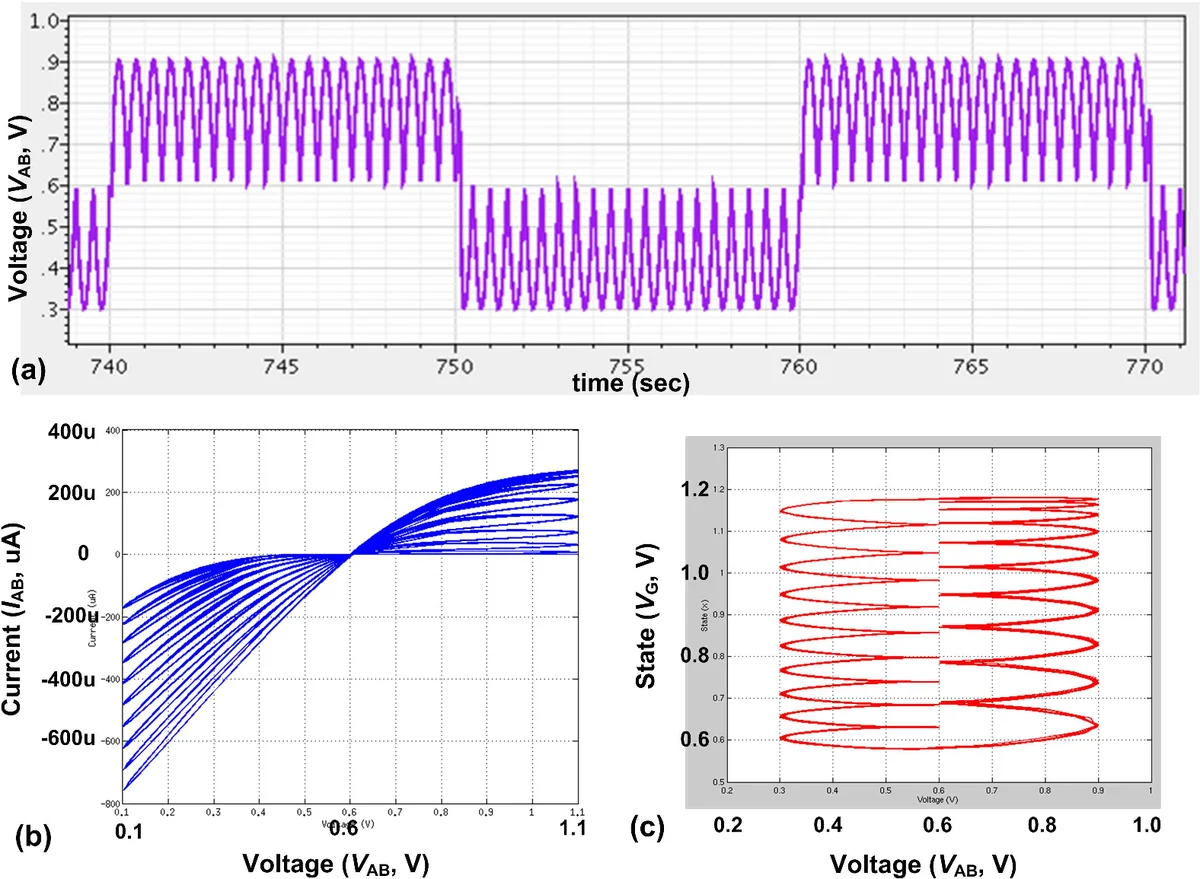

본 논문은 이상적인 메모리스터의 특성을 모방하는 컴팩트한 CMOS 회로를 제안한다. 이 회로는 두 단자 사이의 전압에 의해 제어되는 가변 저항기로, 메모리스터의 ‘상태’는 커패시터에 저장된다. 130nm CMOS 공정에서 설계 및 시뮬레이션된 이 에뮬레이터는 전형적인 찌그러진 히스테리시스 특성을 보여준다. 논문은 이 회로를 활용하여 아날로그 병렬 처리를 이용한 미로 해결이라는 멤컴퓨팅 응용 사례를 제시하며, 신경형태 및 머신러닝 회로에의 적용 가능성을 열어준다.

상세 분석

이 논문의 핵심 기여는 실제 메모리스티브 소자의 물리적 한계(변동성, 낮은 온-저항, 제한적 내구성)를 우회하면서도 그 기능적 핵심을 구현한 CMOS 기반 에뮬레이터 회로를 제안한 점에 있다. 회로의 동작 원리는 간단하면서도 교묘하다. 메인 트랜지스터(M1)를 트라이오드 영역에서 동작시켜 가변 저항을 형성하고, 두 단자 간 전압(V_AB)을 트랜스컨덕터(Gm)로 감지하여 작은 신호 전류를 생성한다. 이 전류는 커패시터(Cm)에 적분되어 게이트 전압(V_G)으로 저장되며, 이 ‘상태’ 전압이 M1의 채널 저항을 실시간으로 제어한다. 이는 메모리스터의 기본 방정식 I = G(x)·V 와 dx/dt = f(V, t)를 정확히 구현한다.

주요 기술적 통찰은 다음과 같다. 첫째, 회로는 표준 CMOS 공정에서 쉽게 구현 가능하며, 메인 트랜지스터의 사이징을 통해 에뮬레이트되는 메모리스터의 저항 범위를 자유롭게 설계할 수 있다는 실용적 장점을 가진다. 이는 실제 메모리스티브 소자가 가진 저항 범위의 제약을 넘어선다. 둘째, 스위치(M_sw)를 도입하여 커패시터의 충전 상태를 유지함으로써 아날로그 메모리 기능(단기 기억)을 구현했다. 이는 메모리스터의 핵심인 ‘기억’ 기능을 회로적으로 모방한 것이다. 셋째, 제시된 미로 해결 네트워크 응용은 이러한 에뮬레이터가 단순한 특성 모방을 넘어, 병렬 아날로그 컴퓨팅(멤컴퓨팅)을 통한 실제 문제 해결에 활용될 수 있음을 보여준다. 네트워크 내 각 메모리스터 셀의 상태 변화를 통해 해답 경로가 ‘밝아지는’ 방식은 본질적으로 아날로그 병렬 처리의 잠재력을 보여준다.

이 접근법의 의의는 메모리스티브 소자 기술이 완전히 성숙하기 전까지 시스템 수준의 신경형태/머신러닝 알고리즘 및 구조를 탐구하고 프로토타이핑할 수 있는 저위험 대안을 제공한다는 점이다. 이는 이론과 실용적인 칩 구현 사이의 간극을 메우는 가교 역할을 한다.

댓글 및 학술 토론

Loading comments...

의견 남기기