제한 메모리 가속기를 활용한 이기종 시스템에서의 효율적인 선형 학습

안내: 본 포스트의 한글 요약 및 분석 리포트는 AI 기술을 통해 자동 생성되었습니다. 정보의 정확성을 위해 하단의 [원본 논문 뷰어] 또는 ArXiv 원문을 반드시 참조하시기 바랍니다.

초록

본 논문은 메모리 용량이 제한된 GPU·FPGA와 같은 가속기와 대용량 메인 메모리를 가진 CPU를 결합한 이기종 환경에서, 좌표별 듀얼리티 갭을 이용해 중요한 데이터 블록을 동적으로 선택하고, 두 장치가 병렬로 작업하도록 설계한 DUHL(Duality‑Gap‑based Heterogeneous Learning) 알고리즘을 제안한다. 이론적으로는 근사 블록 좌표 하강법의 수렴률을 일반화하고, 선택된 블록이 전체 갭에 기여하는 비율(ρ)에 비례해 수렴 속도가 향상됨을 증명한다. 실험에서는 대규모 일반화 선형 모델 학습에서 기존 배치·균등 샘플링 방식 대비 10배 이상 가속을 달성한다.

상세 분석

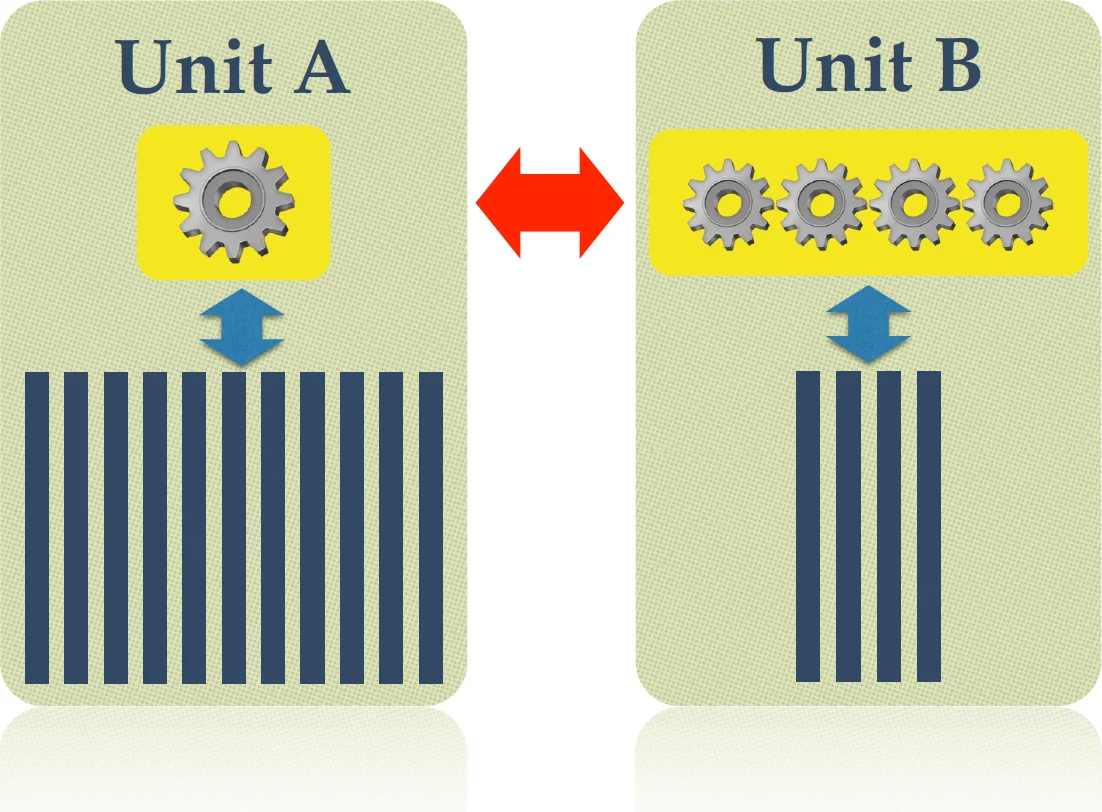

이 논문은 현대의 이기종 컴퓨팅 환경, 특히 메모리 용량이 작은 고성능 가속기와 메모리 용량이 큰 저성능 장치가 동시에 존재하는 상황을 모델링한다. 저자는 먼저 일반화 선형 모델 minα f(Aα)+g(α) 의 프루얼‑듀얼 구조를 이용해 좌표별 듀얼리티 갭 gap_i(α_i) 을 정의하고, 이 값이 해당 좌표가 현재 최적화에 얼마나 기여하는지를 정량화한다는 점을 강조한다.

핵심 이론적 기여는 두 가지이다. 첫째, 기존의 좌표 하강법(특히 SDCA) 분석을 블록 업데이트와 근사(θ‑approximate) 업데이트까지 확장하였다. 여기서 블록 P 의 선택에 따라 ρ_t,P = (∑{j∈P}gap_j)/(∑{j}gap_j) 가 정의되며, 수렴 상수 η_P = min_t θ E

댓글 및 학술 토론

Loading comments...

의견 남기기