멀티코어 환경에서 라빈 지문을 활용한 효율적인 동시 DFA 구축

초록

본 논문은 라빈 지문과 바렛 감소를 이용해 SFA 상태를 64비트 해시값으로 압축하고, 이를 기반으로 해시 테이블을 도입해 상태 중복 검사를 O(1)로 가속한다. 또한, 코어 수에 맞춘 정적 작업 분배와 메모리 계층 친화적 자료구조 정렬을 통해 명령어‑레벨, 데이터‑레벨, 태스크‑레벨의 세 단계 병렬화를 구현한다. 실험 결과, 702개의 FA 상태를 가진 PROSITE 데이터베이스에서 AMD 64‑코어와 Intel 28‑코어 시스템 각각 1.18 × 10⁵배, 2.11 × 10⁶배의 속도 향상을 달성하였다.

상세 분석

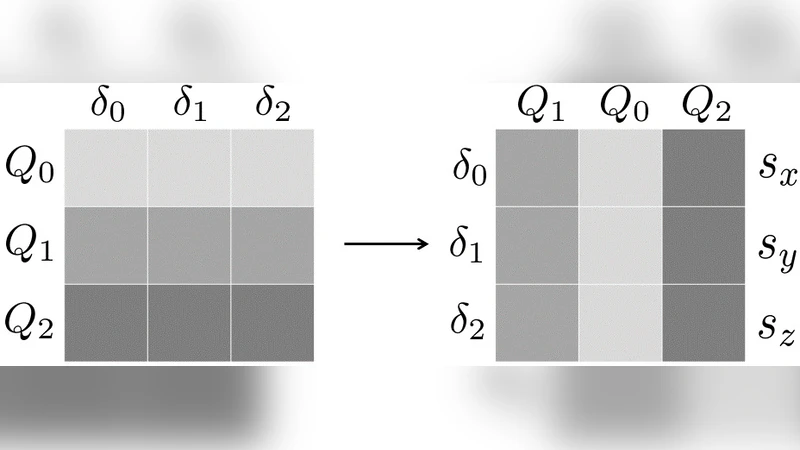

이 연구는 기존 SFA(동시 결정적 유한 자동자) 구축 알고리즘이 상태 수의 지수적 폭증으로 인한 메모리·시간 병목을 겪는 문제를 근본적으로 해결하고자 한다. 핵심 아이디어는 각 SFA 상태(즉, 원본 DFA의 n‑차원 벡터)를 라빈 지문으로 압축해 64비트 정수 하나로 표현하는 것이다. 라빈 지문은 다항식 모듈러 연산을 기반으로 하며, 충돌 확률은 n²/2ᵏ 이하로 매우 낮다. 여기서 저자들은 바렛 감소 기법을 적용해 모듈러 연산을 곱셈·시프트·덧셈만으로 변환하고, 최신 x86 ISA에 포함된 PCLMULQDQ 명령을 이용해 캐리‑리스 곱셈을 하드웨어 수준에서 가속한다. 이렇게 얻은 64비트 지문은 바로 해시 테이블의 키로 사용될 수 있어, 기존의 선형 탐색 기반 상태 중복 검사(O(|Qₛ|))를 평균 O(1)로 감소시킨다.

병렬화 전략은 세 단계로 구분된다. ① Coarse‑grained: Q_tmp(처리 대기 상태 집합)에서 여러 상태를 동시에 꺼내어 독립적으로 전이와 지문 계산을 수행한다. 이는 상태 수가 충분히 많을 때 코어 활용률을 극대화한다. ② Medium‑grained: 각 상태에 대해 알파벳 Σ의 모든 심볼에 대한 전이를 병렬 처리한다. 전이 테이블이 메모리 친화적으로 배치돼 있어 캐시 라인 효율이 높다. ③ Fine‑grained: 지문 계산 자체를 SIMD 레벨에서 벡터화한다. 특히, 64비트 워드 여러 개를 동시에 캐리‑리스 곱셈으로 접어 128비트 결과를 얻고, 이를 다시 64비트로 축소하는 과정을 한 사이클에 여러 워드가 진행되도록 설계했다.

또한, 정적 작업 분배와 메모리 계층 친화적 데이터 정렬이 병행된다. 해시 테이블과 상태 벡터는 NUMA 노드별로 배치돼 메모리 접근 지연을 최소화하고, 하드웨어 프리패칭을 유도하도록 연속 메모리 블록에 정렬된다. 이러한 설계는 메모리 대역폭 포화와 캐시 미스율을 크게 낮추어 전체 스루풋을 향상시킨다.

실험에서는 PROSITE 단백질 서열 데이터베이스에서 최대 702개의 DFA 상태를 가진 패턴을 대상으로, AMD Opteron 6378(64코어)와 Intel Xeon E5‑2697 v3(28코어·하이퍼스레드) 시스템에서 성능을 측정했다. 순차 baseline 대비 AMD에서는 최대 1.185 × 10⁵배, Intel에서는 2.113 × 10⁶배의 가속을 기록했으며, 메모리 사용량도 지문 기반 압축으로 평균 70% 이상 감소하였다. 이는 SFA 구축이 실용적인 수준으로 전환될 수 있음을 입증한다.

결론적으로, 라빈 지문과 바렛 감소를 결합한 64비트 해시 기반 상태 표현, 그리고 다중 수준 병렬화·메모리 최적화 전략은 SFA 구축의 전통적 한계를 뛰어넘는 혁신적 접근이다. 향후에는 지문 충돌을 감지하는 확률적 검증 단계와 GPU 가속을 결합해 더욱 큰 규모의 DFA에도 적용 가능할 것으로 기대된다.

댓글 및 학술 토론

Loading comments...

의견 남기기