동적 데이터 기반 포토닉‑플라스몬 하이브리드 NoC D3NOC

초록

본 논문은 DDDAS(동적 데이터 구동 응용 시스템) 패러다임을 NoC 설계에 적용하여, 전기 메쉬에 광학 익스프레스 버스를 동적으로 삽입하는 하이브리드 포토닉‑플라스몬 네트워크‑온‑칩(D3NOC)을 제안한다. CHyPPI라는 구성 가능한 하이브리드 광학 인터커넥트를 이용해 지연·전력·처리량을 개선하고, 측정 윈도우 길이를 그래디언트 디센트 방식으로 자동 조정한다. NAS Parallel Benchmark와 합성 트래픽을 통해 16×16 전기 메쉬 대비 평균 지연 89%, 동적 전력 67% 향상을 보였다.

상세 분석

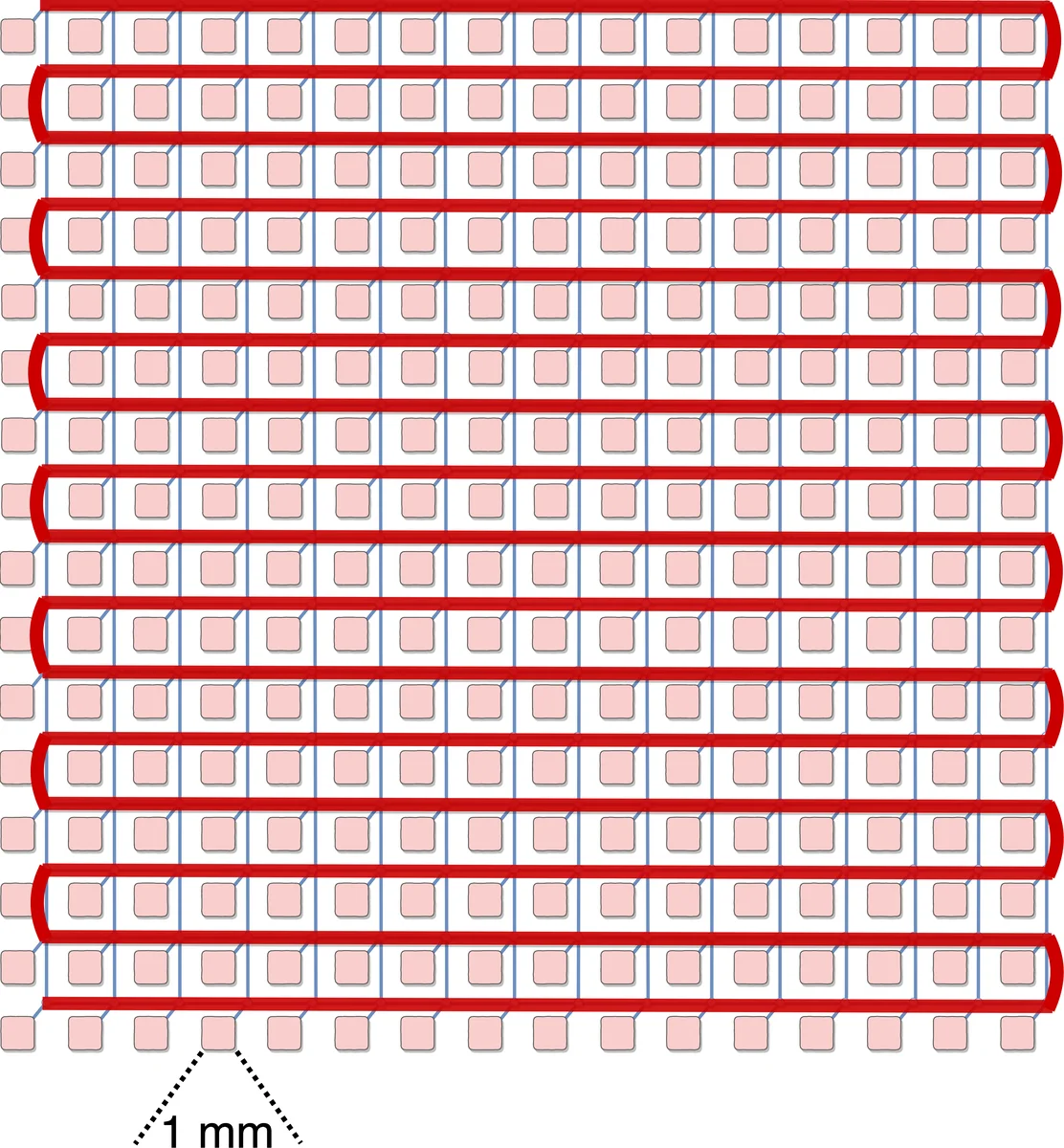

이 연구는 기존 정적 NoC 설계가 애플리케이션의 트래픽 변동에 적응하지 못한다는 한계를 DDDAS 개념으로 극복한다는 점에서 혁신적이다. DDDAS는 측정(measurement)과 계산(computation)이 서로 피드백을 주고받으며 시스템을 실시간으로 최적화한다는 원칙을 갖는다. 논문에서는 이 원칙을 NoC에 적용해 두 가지 동적 요소를 도입한다. 첫 번째는 토폴로지 재구성이다. 기본 16×16 전기 메쉬 위에 전역 광학 익스프레스 버스를 serpentine 형태로 배치하고, 트래픽이 집중되는 원거리 코어 쌍을 실시간으로 선택해 버스에 할당한다. 두 번째는 측정 윈도우 자체를 동적으로 조정한다. 각 코어는 이전 운영 윈도우 동안 가장 많이 통신한 파트너와 전체 플릿 수를 RCU(재구성 제어 유닛)에 보고하고, RCU는 평균 지연을 비용 함수로 삼아 그래디언트 디센트(Gradient Descent) 알고리즘으로 다음 윈도우 길이를 업데이트한다. 이때 윈도우 길이가 너무 짧아 재구성 오버헤드가 커지는 것을 방지하기 위해 최소 100 사이클의 하한을 두었다.

광학 인터커넥트는 CHyPPI(Configurable Hybrid Photonic‑Plasmonic Interconnect)라는 새로운 구조를 사용한다. CHyPPI는 전파 손실이 낮은 포토닉 웨이브가이드를 신호 전송에 이용하고, 플라스몬 스위치를 통해 고속·저전력 변조와 검출을 수행한다. 핵심 소자는 ‘Mo‑detector’로, 2×2 플라스몬 스위치와 그래핀 포토디텍터를 결합해 변조와 검출을 하나의 장치에 통합한다. 실험적 파라미터에 따르면 삽입 손실은 0.08 dB, 소멸비는 15.53 dB, 에너지 효율은 2.59 fJ/bit(전송) 및 0 fJ/bit(검출)이다. 이러한 특성은 전기 라인 대비 50 Gb/s의 높은 대역폭을 제공하면서도 면적·전력 비용을 크게 늘리지 않는다.

시뮬레이션 환경은 11 nm CMOS 기반 DSENT 모델을 수정해 전기·광학 라인의 정적·동적 전력을 추정했으며, 라우터는 5‑포트(전기)와 7‑포트(하이브리드) 구조를 사용했다. 전기 라인 홉당 1클럭, 광학 라인 홉당 2클럭(광‑전 변환 포함) 지연을 적용했으며, 플릿 크기는 64 bit, 클럭 주파수는 0.78125 GHz(광 라인 전송 속도와 일치)로 설정했다.

성능 평가에서는 NAS Parallel Benchmark(NPB) 중 몇 가지 커널과 합성 트래픽을 사용해 평균 지연과 동적 전력을 측정했다. 결과는 D3NOC이 기존 16×16 전기 메쉬 대비 평균 지연을 최대 89 % 감소시키고, 동적 전력 소비를 67 % 절감한다는 점을 보여준다. 특히 트래픽이 고르게 분산된 경우에도 측정 윈도우 자동 조정이 효과적으로 작동해 재구성 오버헤드를 최소화한다. 그러나 설계가 하나의 전역 익스프레스 버스만을 지원하므로, 다중 버스 혹은 다중 경로를 활용한 확장성에 대한 추가 연구가 필요하다. 또한, 광학 장치의 온도·공정 변동에 대한 내성이 논문에 충분히 다루어지지 않아 실제 실리콘 포토닉 구현 시 신뢰성 확보가 과제로 남는다.

요약하면, 이 논문은 DDDAS 기반의 피드백 루프를 NoC에 도입해 토폴로지와 측정 파라미터를 동시에 최적화함으로써, 하이브리드 포토닉‑플라스몬 인터커넥트가 제공하는 고대역폭·저전력 특성을 실시간 시스템 요구에 맞게 활용한다는 중요한 개념을 제시한다. 향후 연구는 다중 버스 설계, 복합 비용 함수(전력·면적·열), 그리고 실리콘 포토닉 공정 변동에 대한 견고한 제어 메커니즘을 포함해 설계 공간을 넓히는 방향으로 진행될 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기