전파 단계 구현 방식 비교와 성능 모델링

초록

본 논문은 격자 볼츠만법(LBM)의 전파 단계 구현 방법을 여러 가지 제시하고, 각 방법이 격자 노드당 필요로 하는 메모리 전송 횟수를 기준으로 비교한다. 메모리 대역폭 기반 성능 모델을 구축해 다양한 CPU 아키텍처에서 이론적 최대 성능을 예측하고, 실제 Intel·AMD 서버에서 벤치마크 결과와 비교한다. 결과적으로 “AA 패턴”·“Esoteric Twist”와 같은 고급 기법이 구현 난이도는 높지만 메모리 전송을 크게 감소시켜 현저히 높은 성능을 달성함을 확인한다.

상세 분석

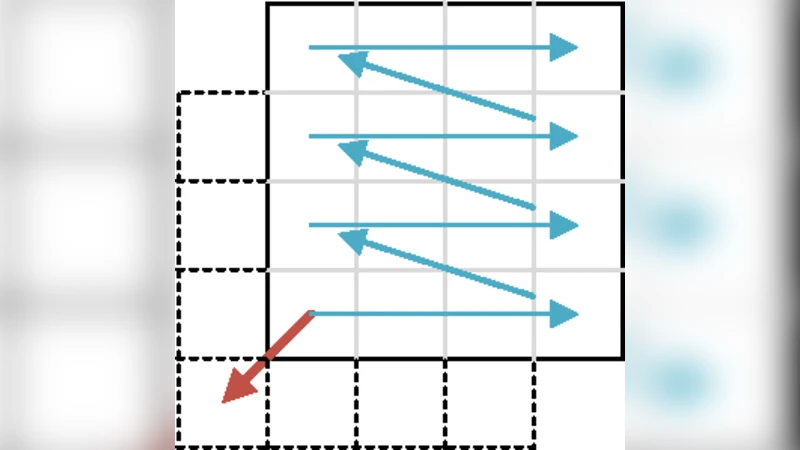

논문은 LBM의 핵심 연산인 충돌‑전파를 두 단계로 나누는 전통적인 두‑스텝(TS) 방식, 충돌과 전파를 하나의 커널에 결합한 원‑스텝(OS) 방식, 그리고 메모리 사용을 최소화하기 위해 격자 자체를 이동시키는 압축 격자(CG) 방식, PDF를 교환하면서 데이터 의존성을 회피하는 스왑(SWAP) 방식, 두 개의 커널을 교대로 호출하는 AA‑패턴, 그리고 포인터 스와핑을 이용해 메모리 접근을 최적화하는 Esoteric Twist 등 총 여섯 가지 전파 구현을 상세히 설명한다. 각 방식에 대해 SoA와 AoS 데이터 레이아웃, 직접 주소화와 간접 주소화(인덱스 배열) 두 가지 메모리 배치를 고려해 메모리 로드·스토어 횟수를 정량화하였다. 예를 들어 TS는 한 노드당 6q PDF 로드와 6q 스토어(간접 주소화 시 추가 IDX 로드·스토어) 등 가장 많은 전송을 요구하는 반면, OS‑NT(Non‑Temporal Store)와 같은 변형은 읽기·쓰기 횟수를 절반 수준으로 줄인다.

성능 모델은 각 CPU의 메모리 대역폭(BW)과 캐시 라인 크기(128 Byte)를 입력으로, 노드당 전송 바이트 수를 곱해 이론적 최대 FLOP/s를 추정한다. 모델은 특히 메모리 대역폭이 병목인 현대 x86 서버에서 정확히 맞아떨어지며, 캐시 친화적인 구현이 아닌 경우(예: 다중 비임시 저장 스트림) 성능 저하가 발생한다는 점을 강조한다. 실험에서는 D2Q9 격자를 사용한 다공성 매체 흐름 시뮬레이션을 기반으로, Intel Xeon E5‑2670, AMD Opteron 6176 등 네 종류의 노드에서 TS, OS, CG, SWAP, AA, Esoteric Twist을 구현해 측정하였다. 결과는 메모리 전송 횟수가 적은 AA‑패턴과 Esoteric Twist이 2배 이상 높은 실측 성능을 보이며, 모델 예측치와도 오차가 5 % 이내에 머물렀다. 또한, 비임시 저장을 활용한 OS‑NT는 메모리 대역폭을 크게 절감했지만, 하드웨어가 지원하는 비임시 스트림 수가 제한적일 경우 오히려 성능이 떨어지는 현상이 관찰되었다.

이러한 분석을 통해 논문은 전파 단계 구현 선택이 메모리 전송 효율에 직접적인 영향을 미치며, 고성능 LBM 코드를 설계할 때는 데이터 레이아웃, 주소화 방식, 그리고 가능한 경우 고급 전파 기법(AA, Esoteric Twist)을 적용하는 것이 필수적임을 결론짓는다.

댓글 및 학술 토론

Loading comments...

의견 남기기