SGX 내부 제어 흐름을 드러내는 브랜치 섀도잉 공격

초록

본 논문은 Intel SGX가 enclave와 비‑enclave 전환 시 브랜치 히스토리를 초기화하지 않는 설계 결함을 이용해, 악성 OS가 브랜치 예측 메커니즘을 측정·조작함으로써 enclave 내부의 세밀한 제어 흐름(조건·간접·무조건 분기)을 실시간으로 추출하는 “branch shadowing” 공격을 제안한다. Intel PT·LBR 기반 히스토리 추론과 APIC 타이머를 활용한 정밀 실행 제어 기법을 결합해 실제 SGX 어플리케이션과 최신 방어 메커니즘을 모두 무력화함을 보이며, 하드웨어·소프트웨어 차원의 완화 방안도 제시한다.

상세 분석

이 논문은 SGX 설계의 미세한 결함을 발견하고, 이를 이용한 새로운 사이드채널 공격인 브랜치 섀도잉(branch shadowing) 공격을 체계적으로 구현한다. SGX는 enclave 모드와 비‑enclave 모드 전환 시 레지스터와 캐시 등은 정리하지만, 브랜치 히스토리(Branch Target Buffer와 내부 히스토리 버퍼)는 그대로 유지한다. 따라서 enclave 내부에서 실행된 분기 명령들의 taken/not‑taken 정보가 CPU 내부에 남아 외부에서 관찰 가능하다.

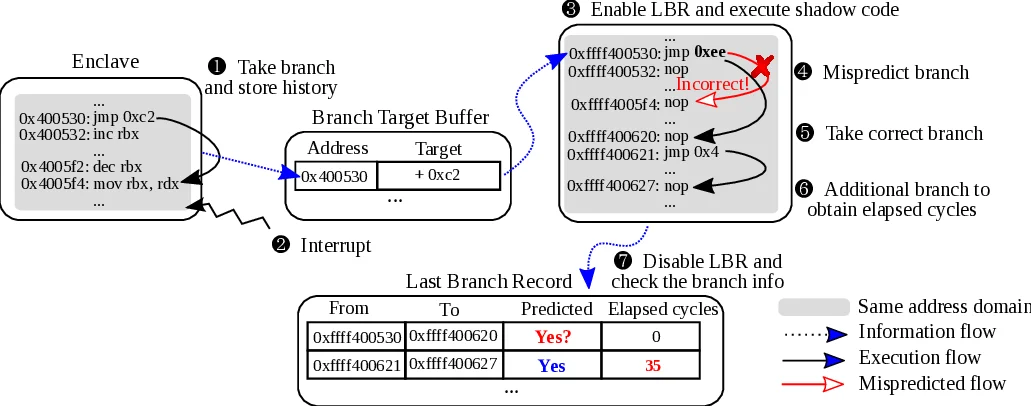

공격자는 두 가지 핵심 기술을 사용한다. 첫째, Intel Processor Trace(PT)와 Last Branch Record(LBR)를 이용해 enclave 내부의 실제 분기 결과를 고정밀 타이밍 없이도 추출한다. LBR은 최근 32개의 분기 정보를 포함해 각 분기의 예측 성공 여부와 두 엔트리 사이의 사이클 수를 제공한다. 특히 Skylake·Kaby Lake에서 제공되는 “timed LBR”은 예측 성공·실패를 직접적으로 노출하므로, 조건부·간접 분기의 실제 흐름을 거의 무노이즈로 복원할 수 있다. 둘째, 로컬 APIC 타이머를 높은 주기로 설정하고 인터럽트 핸들러에 공격 코드를 삽입해 enclave 실행을 정밀하게 중단·재개한다. 이렇게 하면 공격자는 원하는 시점에 enclave 내부의 특정 분기 직후에 LBR을 읽어 히스토리를 캡처할 수 있다. 또한 캐시를 선택적으로 비활성화해 미스프레딕션 패널티를 명확히 측정한다.

브랜치 섀도잉은 기존의 페이지 폴트 기반 “controlled‑channel” 공격보다 훨씬 미세한 granularity를 제공한다. 페이지 수준 접근 패턴만 노출되는 기존 공격과 달리, 이 방법은 기본 블록 단위, 즉 각 분기의 taken 여부까지 드러낸다. 이는 ORAM, Sanctum, SGX‑Shield, T‑SGX와 같은 최신 방어 메커니즘이 가정한 공격 표면을 완전히 무력화한다. 논문은 RSA 비밀키, 머신러닝 모델 파라미터, 웹 서버 요청 등 실제 어플리케이션에서 민감 정보를 추출한 사례를 제시한다.

완화 방안으로는 하드웨어 수준에서 enclave 전환 시 BTB·브랜치 히스토리를 강제로 클리어하는 설계를 제안하고, 소프트웨어 수준에서는 “Zigzagger”라는 변형 컴파일러 패스와 런타임 기법을 도입한다. Zigzagger는 각 분기 뒤에 무작위화된 indirect branch를 삽입해 BTB 충돌을 방지하고, 다중 타깃 indirect branch를 활용해 예측 정확도를 낮춘다. 실험 결과 두 방안 모두 평균 1.2배 이하의 성능 오버헤드로 충분히 실용적임을 보인다.

이 연구는 SGX가 제공하는 “하드웨어 격리”가 내부 마이크로아키처 상태까지 보호하지 못한다는 점을 강조하며, 향후 설계 시 마이크로아키처 레벨의 사이드채널을 고려한 전면적인 검증이 필요함을 역설한다.

댓글 및 학술 토론

Loading comments...

의견 남기기