HPC 정확성 위기와 차세대 검증·디버깅 로드맵

초록

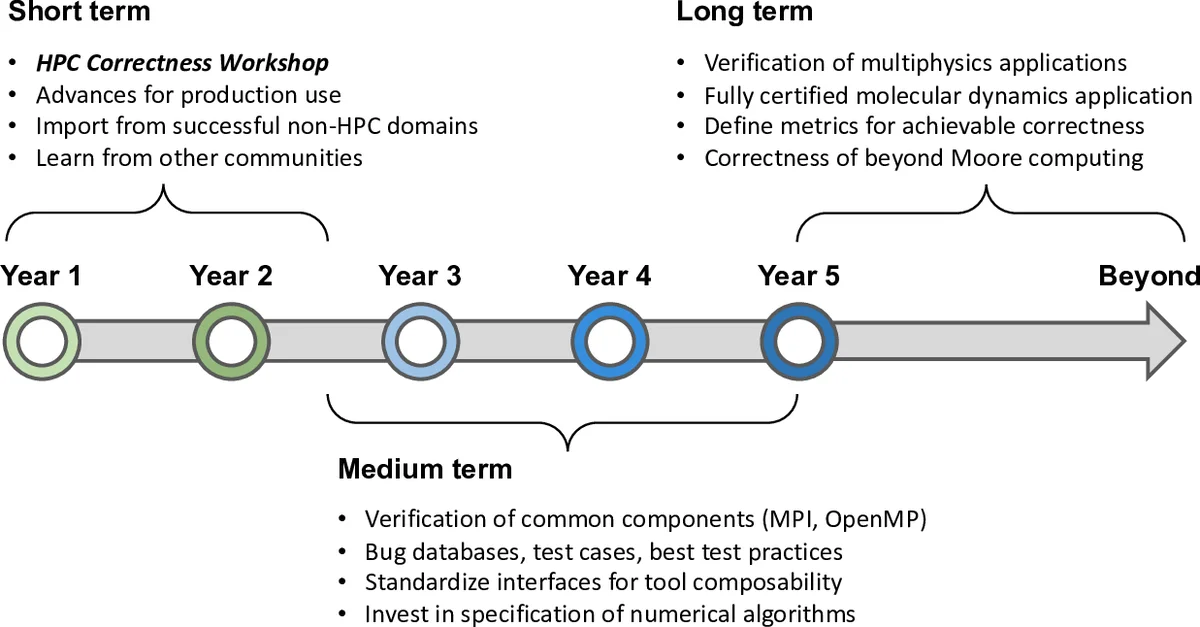

본 보고서는 고성능 컴퓨팅(HPC) 환경에서 급증하는 버그와 복잡성으로 인한 ‘정확성 위기’를 진단하고, 정적·동적 분석, 형식 검증, 비정형 디버깅 등 4대 연구축을 제시한다. 단기·중기·장기 로드맵을 통해 exascale 시대에 필수적인 자동화·형식화 도구 개발을 촉구한다.

상세 분석

보고서는 먼저 이질적인 하드웨어(CPU·GPU·Xeon‑Phi·비휘발성 메모리 등)와 대규모 동시성(수십만 MPI 프로세스)으로 인해 기존 디버깅 기법이 한계에 봉착했음을 강조한다. 이질성은 메모리 대역폭·연산 속도·전압·주파수 제어까지 다양하게 변동되며, 이러한 변동이 부동소수점 연산 오차와 비결정성을 유발해 재현이 어려운 버그를 만든다. 특히, ‘비직관적 행동’(예: 전압·주파수 스케일링에 따른 연산 결과 변동)과 ‘인지 과부하’(다중 프로그래밍 모델·동적 런타임·코드 자동 생성 등) 때문에 인간이 직접 원인을 파악하기 힘들다.

핵심 기술적 통찰은 다음과 같다. 첫째, 정밀 사양(specification)과 검증(verification) 사이의 격차를 메타모델링과 형식적 사양 언어로 메꾸어야 한다. 둘째, 정적 분석은 컴파일 타임에 메모리 일관성, MPI 태그 사용, 연산 정확도 등을 검증하고, 동적 분석은 실행 시 비결정적 경로를 추적해 레이스 컨디션·데드락을 자동 탐지한다. 셋째, 기존 디버거가 제공하지 못하는 ‘스케일‑인‑시뮬레이션’(대규모 노드에서 재현 가능한 오류 재현)과 ‘비정형 로그 기반 이상 탐지’를 결합한 하이브리드 프레임워크가 필요하다. 넷째, 검증 가능한 라이브러리·컴파일러·런타임을 구축하기 위해 ‘컴파일러·라이브러리 검증’ 전용 베이스라인을 마련하고, 이를 오픈소스 형태로 공유해야 한다.

연구 로드맵은 1‑2년 내에 정적 분석 도구와 동적 레이스 탐지기 프로토타입을 배포하고, 2‑5년 안에 형식 검증 기반 컴파일러·라이브러리 인증 체계를 구축한다. 5년 이상 장기 목표는 완전 인증된 응용 프로그램(예: 분자동역학·멀티피직스)과 검증 대회·워크숍을 통해 커뮤니티 전체에 검증 문화와 인프라를 정착시키는 것이다.

댓글 및 학술 토론

Loading comments...

의견 남기기