고유전율 게이트 NMOS 트랜지스터 시간 제로 변동과 노화 효과 연관성 분석

초록

본 논문은 30 nm 기술 노드의 고유전율 금속 게이트 NMOS 트랜지스터에서 랜덤 도펀트 변동(RDF)이 BTI에 미치는 영향을 시뮬레이션 기반으로 조사한다. 작은 면적(≈1000 nm²) 디바이스에서 RDF가 Vth 변동을 크게 확대함을 확인했으며, 회로 수준에서도 성능 저하가 유사하게 나타난다. 반면 TDDB와 SILC는 RDF에 대한 민감도가 낮아 약한 상관관계만을 보였다. 결과는 스케일링된 공정에서 RDF를 고려한 변동 내성 설계가 필요함을 시사한다.

상세 분석

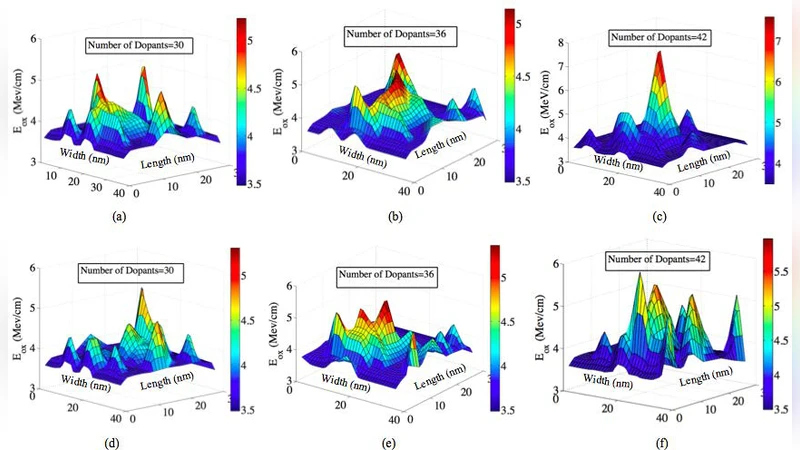

본 연구는 고유전율(High‑κ) 금속 게이트(NMOS) 트랜지스터에서 시간 제로 변동, 특히 랜덤 도펀트 변동(RDF)이 시간 의존성 열 불안정성(BTI) 및 연관된 노화 메커니즘에 미치는 영향을 정량적으로 평가한다. 30 nm 공정 노드의 1000 nm² 정도의 작은 면적을 갖는 디바이스를 대상으로, Monte‑Carlo 기반의 TCAD 시뮬레이션 프레임워크를 구축하였다. 여기서는 도펀트 입자 수와 위치를 확률적으로 배치하여 각 샘플에 대한 초기 문턱 전압(Vth) 분포를 생성하고, 이후 동일한 전압·온도 스트레스를 가해 BTI에 의한 ΔVth를 추적한다. 시뮬레이션 결과, RDF가 초기 Vth 분포를 넓히는 동시에, 낮은 Vth(빠른 스위칭) 영역에 위치한 디바이스가 더 높은 전기장에 노출되어 BTI 가속화가 발생한다는 사실이 밝혀졌다. 이는 ΔVth의 표준편차 σΔVth가 초기 Vth 변동 σVth와 거의 선형적인 상관관계를 보이며, 특히 σVth가 10 mV 수준을 초과할 경우 σΔVth는 30 % 이상 증가한다는 정량적 결과로 나타난다. 회로 수준에서는 이러한 Vth 변동이 게이트 지연과 전력 소모에 직접적인 영향을 미쳐, 동일한 설계 마진을 적용했을 때 최악의 경우 15 % 이상의 타이밍 오버헤드가 발생한다. 반면, 시간 의존성 유전 파괴(TDDB)와 스트레스 유도 누설 전류(SILC)는 전계와 온도에 크게 의존하지만, 초기 도펀트 배치에 의한 변동은 미미하였다. 구체적으로, TDDB의 고장 시간(tBD)와 SILC의 전류 증가율은 RDF가 포함된 경우와 제외된 경우 사이에 통계적으로 유의미한 차이가 없었으며, 이는 전계 집중 현상이 주된 메커니즘임을 시사한다. 종합적으로, 본 연구는 스케일링이 진행될수록 RDF가 BTI 변동을 주도하는 핵심 요인으로 부상함을 강조하고, 설계 단계에서 초기 변동을 고려한 마진 설정 및 보정 회로 도입이 필요함을 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기