텐서 연산을 활용한 고차원 EDA 문제 해결

본 논문은 전자설계자동화(EDA) 분야에서 차원 저주에 시달리는 고차원 문제들을 효율적으로 다루기 위한 일반적인 프레임워크로서 텐서 연산을 제시한다. 텐서의 기본 개념, 주요 분해·완성 기법을 튜토리얼 형식으로 소개하고, 비선형 회로 모델링과 고차원 불확실성 정량화 등 최신 적용 사례를 통해 효용성을 입증한다. 또한 향후 연구가 필요한 개방형 문제들을 제시한다.

저자: Zheng Zhang, Kim Batselier, Haotian Liu

이 논문은 전자설계자동화(EDA) 분야에서 차원 저주(curse of dimensionality) 문제를 해결하기 위한 새로운 수학적 프레임워크로 텐서 연산을 제안한다. 서론에서는 전통적인 행렬·벡터 기반 알고리즘이 3‑D 필드 솔버, 다중 시간 스케일 회로 시뮬레이션, 확률적 잡음 해석, 다중 파라미터 모델 차원 축소, 설계 공간 탐색, 변동성‑인식 설계 자동화 등 다양한 고차원 문제에서 메모리와 연산 복잡도가 급격히 증가하는 현상을 상세히 기술한다. 특히, 각 문제를 수학적으로 표현했을 때 변수·샘플 수가 n₁·n₂·…·n_d 와 같이 지수적으로 늘어나며, 기존 O(N) 혹은 O(N log N) 복잡도의 선형 솔버조차도 실용적인 한계를 초과한다는 점을 강조한다.

본 논문의 핵심 아이디어는 텐서를 “고차원 배열”로서 직접 다루는 것이다. 텐서는 d‑차원 데이터 구조로, 각 차원(모드)을 독립적으로 처리할 수 있는 k‑모드 곱, 텐서 내적, 외적 등의 연산을 제공한다. 이러한 연산은 행렬·벡터 연산의 일반화이며, 고차원 데이터의 구조적 특성을 보존하면서도 효율적인 계산을 가능하게 한다.

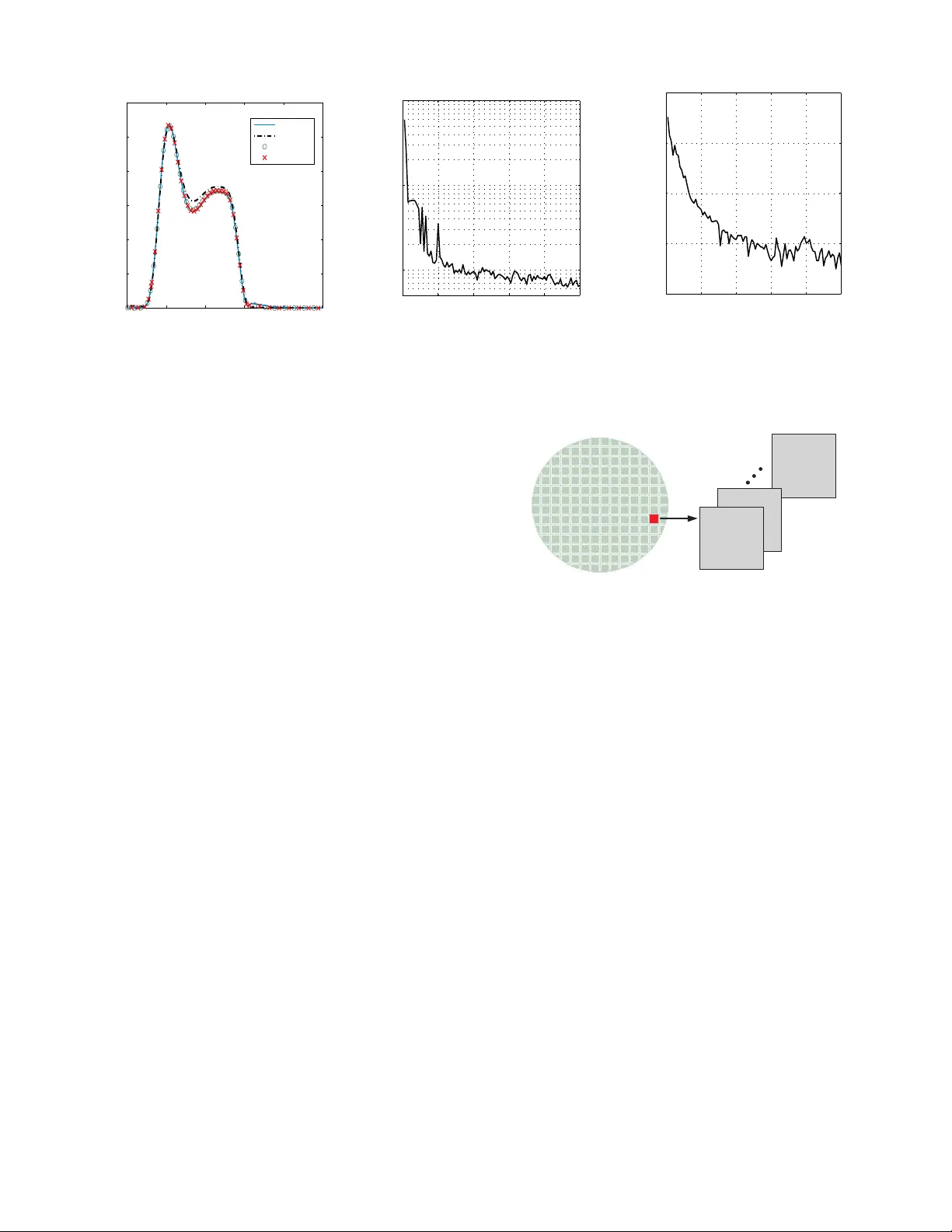

논문은 두 가지 주요 텐서 기법을 중심으로 전개된다. 첫 번째는 **텐서 분해**이며, 여기서는 CPD(Canonical Polyadic Decomposition), Tucker 분해, Tensor‑Train(TT) 분해를 상세히 소개한다. CPD는 텐서를 r개의 rank‑1 텐서(외적)의 합으로 표현하며, 최소 r(텐서 랭크)을 찾는 것이 NP‑hard이지만, ALS(Alternating Least Squares)와 같은 휴리스틱 알고리즘으로 근사 해를 구한다. Tucker 분해는 코어 텐서와 각 모드별 팩터 행렬을 도입해 차원을 축소하고, 코어 텐서의 차원을 조절함으로써 압축률을 조절한다. TT 분해는 텐서를 일련의 3‑차원 코어 텐서(“TT‑cores”)로 연결하는 방식으로, 연산 복잡도가 O(d·n·r²) 로 선형에 가깝게 유지된다. 표 1에서는 세 분해 방식의 저장 비용과 연산 복잡도를 비교해, 특히 TT가 고차원 적분·컨볼루션 연산에서 O(n^d) → O(d·n·r²) 로 급격히 감소함을 보여준다.

두 번째는 **텐서 완성**이다. 관측되지 않은 원소가 다수인 경우, 저랭크 가정을 이용해 전체 텐서를 복원한다. 이는 행렬 완성의 텐서 확장으로, ALS, ADMM, Gradient Descent 기반 알고리즘이 제시된다. 논문은 완성 문제의 이론적 복원 조건(예: incoherence, 샘플 복잡도)과 실제 회로 시뮬레이션에서의 적용 사례를 제시한다. 특히, 확률적 회로 시뮬레이션에서 수천 개의 Monte‑Carlo 샘플 대신 수백 개의 텐서 샘플만으로도 정확한 통계량을 얻을 수 있음을 실험적으로 입증한다.

응용 사례는 두 가지로 구체화된다. 첫 번째는 **비선형 회로 모델링**이다. 비선형 회로의 다항 테일러 또는 볼테라 시리즈 계수를 d‑차원 텐서로 구성하고, TT 분해를 적용해 메모리 사용량을 수십 배 감소시키면서도 실시간 시뮬레이션이 가능하도록 만든다. 두 번째는 **고차원 불확실성 정량화**이다. 다변량 확률 변수의 다항 chaos 전개를 텐서 형태로 표현하고, CPD를 이용해 차원 저주 없이 고차원 확률 분포의 평균·분산·고차 모멘트를 정확히 계산한다. 두 사례 모두 기존 Monte‑Carlo 대비 10~100배 이상의 속도 향상과 메모리 절감 효과를 보인다.

마지막으로 논문은 앞으로의 연구 방향을 네 가지로 제시한다. (1) 텐서 순위 추정 및 동적 업데이트 기법 개발 – 실시간 설계 루프에서 텐서 구조가 변할 때 효율적인 재분해 방법 필요. (2) 하이브리드 텐서‑그래프 최적화 – 텐서 연산과 기존 그래프 기반 EDA 흐름을 결합해 전체 플로우를 최적화. (3) 하드웨어 가속 – GPU, FPGA, ASIC 등에서 텐서 연산을 네이티브하게 지원하는 커스텀 커널 설계. (4) 이론적 복원 한계와 오류 전파 분석 – 텐서 완성 시 발생하는 근사 오차가 회로 시뮬레이션 결과에 미치는 영향을 정량화하는 연구 필요. 이러한 과제들을 통해 텐서 연산이 EDA 전반에 걸쳐 차원 저주를 극복하는 핵심 기술로 자리매김할 수 있음을 강조한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기