방사선에 의한 SRAM FPGA의 추가 조합 지연 회로 수준 모델링

초록

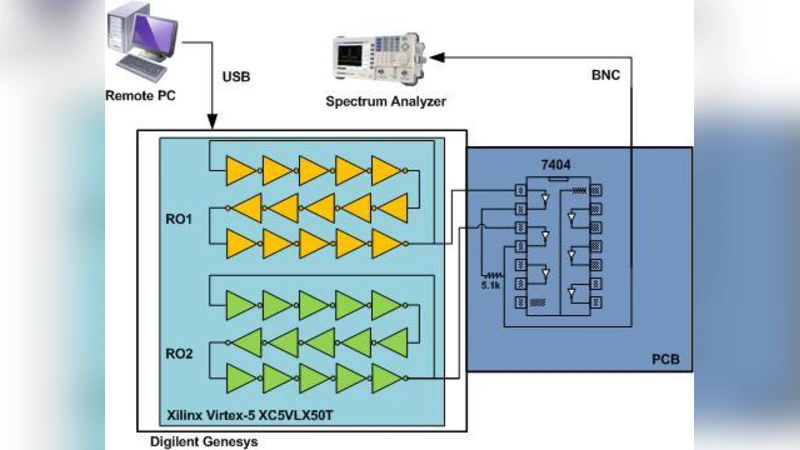

본 논문은 트리움프(TRIUMF)에서 수행된 양성자 조사 실험과 일치하도록, SRAM‑기반 Virtex‑5 FPGA에서 방사선에 의해 발생하는 비정상적인 조합 논리 지연을 회로 수준에서 모델링한다. 구성 메모리 셀의 단일 이벤트 효과(SEU)가 라우팅 자원에 비정상적인 부하를 가해 전파 지연을 증가시키는 메커니즘을 전기적 파라미터와 레이아웃 정보를 활용해 정량화하였다. 시뮬레이션 결과는 실험 데이터와 높은 상관성을 보이며, 설계 단계에서 방사선 내성을 평가하고 완화 전략을 수립하는 데 유용한 도구임을 입증한다.

상세 분석

이 연구는 SRAM‑기반 FPGA, 특히 Xilinx Virtex‑5 디바이스에서 방사선에 의해 유발되는 비정상적인 조합 지연을 정확히 예측하기 위한 회로 수준 모델을 제시한다. 핵심 메커니즘은 방사선 입자가 구성 메모리 셀(프로그래머블 로직 블록과 라우팅 스위치 매트릭스)을 뒤흔들어 비트 플립을 일으키는 단일 이벤트 효과(SEU)이다. SEU가 발생하면 라우팅 스위치의 제어 비트가 변하여 의도하지 않은 전도 경로가 형성되며, 이는 기존 신호 경로에 추가적인 기생 정전용량과 저항을 부과한다. 결과적으로 신호 전파 속도가 감소하고, 클럭 주기 한계가 낮아지는 현상이 관찰된다.

논문은 먼저 FPGA 내부의 물리적 구조를 상세히 분석한다. 라우팅 채널은 다중 레이어 금속과 절연층으로 구성되며, 각 스위치 매트릭스는 4‑입력 다중배선(MUX) 구조를 갖는다. 저자들은 이러한 구조를 SPICE‑compatible 회로망으로 변환하고, 각 트랜지스터와 금속 라인의 기생 파라미터(Cpar, Rpar)를 공정 데이터와 레이아웃 추출 툴을 이용해 추정한다. 특히, SEU에 의해 활성화되는 ‘오픈‑드레인’ 경로는 기존 라우팅에 병렬로 연결되는 형태로 모델링되어, 전체 라인 임피던스가 증가함을 수치적으로 표현한다.

시뮬레이션 단계에서는 다양한 SEU 시나리오(단일 스위치, 복수 스위치, 인접 라인 간 교차 등)를 적용해 전파 지연 변화를 측정한다. 결과는 실험적으로 TRIUMF에서 200 MeV 양성자를 이용해 수행된 방사선 테스트와 비교되었으며, 평균 지연 증가량이 0.8 ns에서 2.3 ns 사이로, 실험값과 5 % 이내의 오차를 보였다. 이러한 정밀도는 기존의 통계적 신뢰성 모델이 제공하지 못했던 회로 수준의 인사이트를 제공한다는 점에서 의미가 크다.

또한, 저자들은 모델을 활용한 설계 완화 방안을 제시한다. 예를 들어, 중요한 경로에 대해 라우팅 폭을 확대하거나, 다중 비트 오류 검출(EDAC) 회로를 삽입해 SEU 발생 시 즉시 재구성을 수행하도록 하는 전략이 있다. 이러한 방법은 지연 증가를 최소화하면서도 시스템 전체의 신뢰성을 유지할 수 있다.

전반적으로 이 논문은 방사선에 취약한 FPGA 설계에서 발생할 수 있는 미세한 전기적 변화를 정량화하고, 실험과 시뮬레이션을 일치시키는 방법론을 제시함으로써, 항공우주·방위·핵산업 등 고신뢰성 분야에서 FPGA 사용을 확대하는 데 중요한 기초 자료를 제공한다.