블록 페이딩 채널을 위한 전밀도 파리티 검사 코드 설계

본 논문은 블록 페이딩(Non‑ergodic Block‑Fading) 채널에서 반복(Iterative) 디코딩이 가능한 저밀도 파리티 검사(LDPC) 코드를 설계하는 방법을 제시한다. 최대우도(ML) 디코딩 기준으로는 설계가 간단하지만, 실제 반복 디코딩에서는 전통적인 ML‑설계 LDPC가 전다양성(full‑diversity)을 상실한다. 이를 극복하기 위해 저자들은 ‘루트 체크노드(root‑check)’를 이용한 새로운 LDPC 구조인 ‘루트…

저자: Joseph J. Boutros, Albert Guillen i Fabregas, Ezio Biglieri

본 논문은 비에르고딕 블록 페이딩(Block‑Fading, BF) 채널에서 저밀도 파리티 검사(Low‑Density Parity‑Check, LDPC) 코드를 설계하는 문제를 다루며, 특히 반복(Iterative) 메시지 전달 디코딩을 적용했을 때의 성능을 중점적으로 분석한다.

1. **채널 모델 및 기본 개념**

BF 채널은 코드워드가 n_c 개의 블록으로 나뉘며, 각 블록은 독립적인 페이딩 계수 α_j 를 가진다. 채널은 비에르고딕이므로 전통적인 용량 개념이 무의미하고, 대신 아웃지 확률(Outage Probability) P_out(γ,R) 가 성능 한계가 된다. 블록 다이버시티 d 는 코드워드가 최소 d개의 블록에 비제로 비트를 포함하는 정도를 나타내며, 최대 다이버시티는 n_c 로 제한된다. 블록‑와이즈 최소 거리(ω_min) 가 0보다 크면 ‘전다이버시티(full‑diversity)’ 라고 정의한다.

2. **ML 디코딩 기반 설계와 한계**

먼저 저자들은 ML 디코딩을 가정한 설계 기준을 제시한다. parity‑check 행렬 H 를 H_1,…,H_{n_c} 로 분할했을 때, 각 서브 행렬이 full‑rank이면 전다이버시티가 보장된다. 이를 통해 R ≤ 1/n_c 인 경우에 전다이버시티를 달성할 수 있음을 증명한다. 또한, ω_min 을 2 혹은 3 로 높이기 위해서는 행렬에 추가적인 제약(예: 짝수/홀수 가중치 열, 해밍 코드 삽입 등)을 두어 코드율을 약간 낮추어야 함을 제시한다.

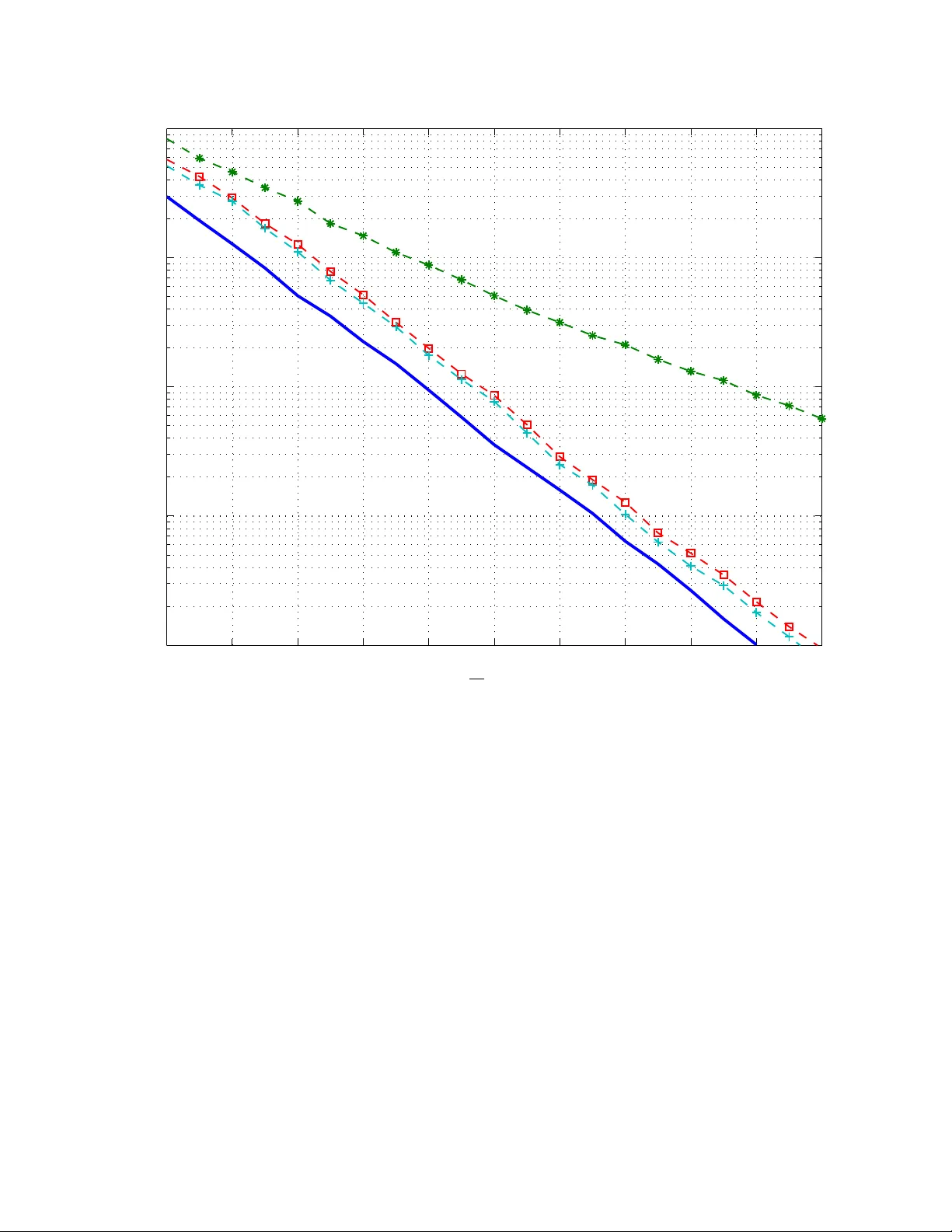

그러나 이러한 ML‑설계 LDPC 코드를 실제 반복 BP( belief‑propagation ) 디코더에 적용하면 pseudo‑codeword 현상으로 인해 블록 다이버시티가 1로 감소한다. 즉, 특정 블록에만 연결된 체크노드가 존재하면 해당 블록이 깊게 페이딩될 때 메시지 전달이 차단되어 디코딩이 실패한다. 실험 결과는 Fig.5 에서 확인할 수 있듯이, ML‑설계 코드가 반복 디코딩을 사용하면 아웃지 한계와 큰 격차를 보인다.

3. **루트 체크노드와 루트 LDPC 설계**

위 문제를 해결하기 위해 ‘루트 체크노드(root‑check)’라는 새로운 체크노드 유형을 도입한다. 루트 체크노드는 하나의 변수노드가 특정 블록에, 나머지 변수노드가 다른 블록에 연결되는 구조이며, 이는 블록 간에 정보를 교환하도록 강제한다. 저자들은 n_c = 2 인 경우를 중심으로 설계 과정을 상세히 설명한다.

- **그래프 구성**: 전체 Tanner 그래프를 ‘루트 체크노드’와 일반 체크노드로 구성한다. 루트 체크노드의 비율을 적절히 조정하면, 각 블록에 속한 변수노드가 최소 하나의 루트 체크노드에 연결되도록 보장한다.

- **밀도 진화 분석**: 블록‑에러 채널(α ∈ {0,∞})을 한계 경우로 두고, 루트 LDPC 그래프에 대한 로그‑비율 확률밀도 진화(LLR‑density evolution)를 수행한다. 분석 결과, 루트 체크노드가 포함된 그래프는 블록 다이버시티 n_c 를 유지하면서도 수렴 임계값이 크게 개선됨을 확인한다.

- **Rayleigh BF 채널 시뮬레이션**: 실제 Rayleigh 페이딩을 가정한 시뮬레이션에서, 루트 LDPC 코드는 아웃지 확률에 근접한 FER(Frame Error Rate) 곡선을 보이며, 기존 (3,6) 정규 LDPC 혹은 ML‑설계 LDPC보다 3~5 dB 이득을 제공한다.

4. **비교 및 실용적 의의**

기존 연구에서는 병렬 터보 코드에 적절한 퍼뮤테이션을 적용하거나, 멀티플렉서 구조를 사용해 전다이버시티를 달성하려 했다. 그러나 이러한 방법은 구현 복잡도가 높거나, 짧은 블록 길이에서 성능이 급격히 저하되는 문제가 있었다. 루트 LDPC는 단순한 체크노드 구조만으로도 전다이버시티를 보장하고, 반복 디코딩에 최적화된 메시지 전달을 가능하게 하여, 복잡도와 성능 사이의 균형을 크게 개선한다.

5. **결론**

저자들은 블록 페이딩 채널에서 반복 디코딩이 가능한 전다이버시티 LDPC 코드를 설계하기 위해 ‘루트 체크노드’를 도입하고, 이를 기반으로 한 루트 LDPC 구조가 이론적 아웃지 한계에 근접하는 실용적인 성능을 제공함을 입증한다. 또한, 설계 방법을 일반적인 (d_v, d_c) 정규 LDPC와 결합하여 다양한 코드율 및 블록 수에 적용 가능함을 보여준다. 향후 연구에서는 다중 안테나(MIMO) 환경이나 고차 변조 방식에 대한 확장, 그리고 하드웨어 구현 최적화가 기대된다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기