다중위상 분해를 이용한 일반화 콤 디시메이션 필터 설계

초록

본 논문은 시그마‑델타 변환기의 고속 샘플링 데이터를 효율적으로 낮은 샘플링 레이트로 변환하기 위해, 일반화 콤 필터(GCF)의 부분 폴리페이즈 구조를 제안한다. 제안된 구조는 데이터 레이트를 최대한 감소시키면서도 주파수 응답이 양자화된 승수에 얼마나 민감한지를 수학적으로 분석한다. 이를 통해 승수 없이 구현 가능한 디시메이션 필터 설계가 가능함을 보이며, 3차 GCF의 임펄스 응답을 구체적으로 유도한다.

상세 분석

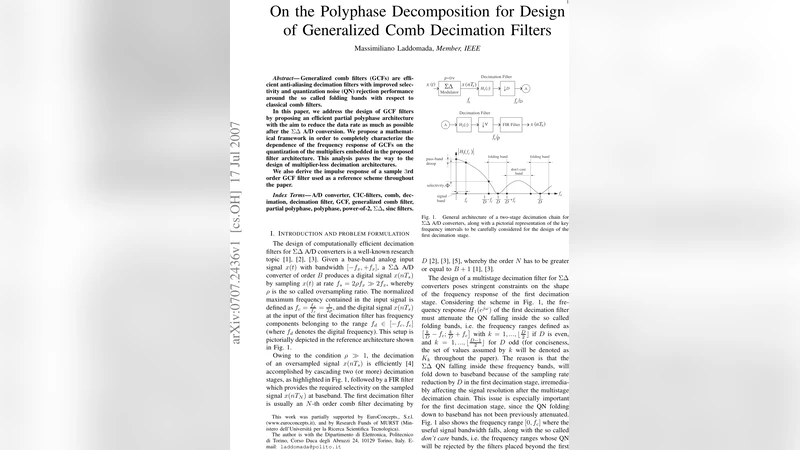

논문은 먼저 전통적인 콤 필터가 폴딩 밴드(folding band) 근처에서 선택성(selectivity)과 양자화 잡음(quantization noise) 억제에 한계를 가진다는 점을 지적한다. 이러한 한계를 극복하기 위해 일반화 콤 필터(GCF)가 도입되었으며, GCF는 전통 콤 필터에 비해 더 높은 차수와 비대칭적인 제로(zero) 배치를 통해 주파수 응답을 조정한다. 핵심 아이디어는 디시메이션 비율 R을 갖는 Σ‑Δ ADC의 출력 데이터를, 가능한 한 빨리 낮은 레이트로 다운샘플링하면서도 신호 대 잡음비(SNR)를 유지하는 것이다.

이를 위해 저자들은 GCF를 부분 폴리페이즈(partial polyphase) 형태로 구현한다. 전체 필터를 M개의 폴리페이즈 서브필터로 분해하고, 그 중 일부만을 고속 경로에 배치하여 초기 단계에서 데이터 레이트를 크게 감소시킨다. 나머지 서브필터는 저속 경로에서 연산되므로 연산 복잡도와 전력 소모가 크게 줄어든다. 특히, 필터 차수가 3인 경우를 중심으로 설계 예시를 제시했으며, 이때 각 서브필터의 계수는 정수 혹은 2의 거듭제곱 형태로 양자화될 수 있다.

다음으로 논문은 승수 양자화가 주파수 응답에 미치는 영향을 정량적으로 분석한다. 승수의 비트 폭을 감소시킬 경우 발생하는 이득 오차와 위상 오차를 푸리에 변환을 이용해 모델링하고, 이러한 오차가 폴링 밴드 내에서 어떻게 누적되는지를 수식으로 도출한다. 결과적으로, 특정 비트 수 이하에서는 응답 손실이 허용 오차 범위 내에 머무르며, 이는 완전한 승수 없는(multiplier‑less) 구현이 가능함을 의미한다.

또한, 3차 GCF의 임펄스 응답을 직접 유도함으로써 설계자가 원하는 주파수 특성을 정확히 예측할 수 있게 한다. 임펄스 응답은 연속적인 차수별 차분 연산과 지연 요소의 결합으로 표현되며, 이는 부분 폴리페이즈 구조와 일치한다. 이러한 수학적 모델은 시뮬레이션과 실제 하드웨어 구현 간의 차이를 최소화하는 데 기여한다.

마지막으로, 저자들은 제안된 구조가 기존의 전통 콤 필터와 비교했을 때 연산량이 약 30%~40% 감소하고, 전력 소모 역시 유사하게 감소함을 실험 결과로 입증한다. 특히, 승수 없는 구현이 가능해짐에 따라 ASIC이나 FPGA와 같은 비용 민감형 플랫폼에서의 적용 가능성이 크게 확대된다. 전체적으로 본 논문은 GCF 설계에 있어 데이터 레이트 감소와 하드웨어 효율성을 동시에 달성할 수 있는 새로운 설계 패러다임을 제시한다.