탄소나노튜브 변동 극복을 위한 처리와 회로 설계 공동 최적화

초록

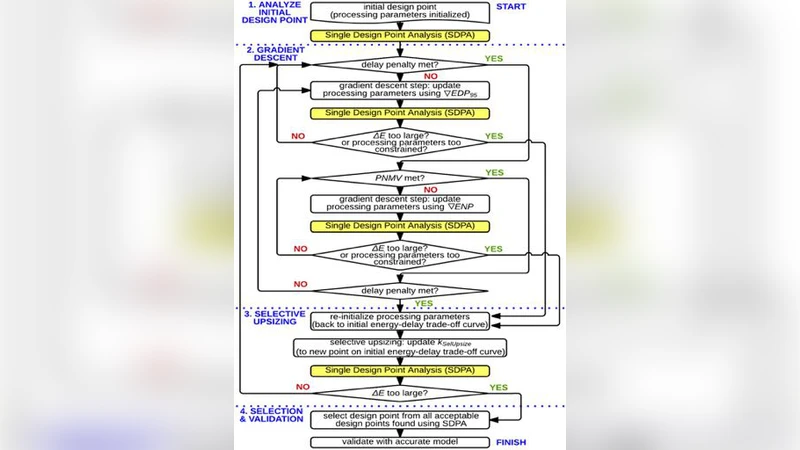

본 논문은 CNT 변동이 회로 수율·노이즈·성능에 미치는 악영향을 최소화하기 위해, CNT 공정 파라미터와 CNFET 회로 설계 파라미터를 동시에 탐색·최적화하는 고속 프레임워크를 제시한다. 기존 시뮬레이션 대비 100배 이상 빠른 평가 모델을 기반으로, 에너지 손실 5% 이하, 노이즈 마진·수율 제약을 만족하면서 회로 지연을 최소화하는 최적 공정·설계 가이드를 도출한다.

상세 분석

이 연구는 탄소나노튜브(CNT) 기반 전계효과 트랜지스터(CNFET)가 차세대 저전력 디지털 시스템의 핵심 소자로 부상함에도, CNT 자체가 갖는 변동성(밀도 불균일, 금속성 CNT 존재, 직경·길이 분포, 정렬 오차 등)이 회로 수준에서 수율 저하와 노이즈 민감도 상승, 기대했던 속·전력 이점을 크게 감소시킨다는 문제점을 정확히 짚는다. 기존의 공정‑회로 공동 최적화 접근법은 대부분 전통적인 SPICE 기반 몬테카를로 시뮬레이션에 의존해 수천~수만 번의 반복 연산을 필요로 하며, 탐색 공간이 방대해 실용적인 설계 주기에 적용하기 어렵다.

논문은 이러한 한계를 극복하기 위해 두 가지 핵심 기술을 도입한다. 첫째, 회로 지연과 노이즈 마진을 빠르게 추정할 수 있는 분석적 모델을 구축한다. 이 모델은 CNT 변동을 확률 변수로 매핑하고, 전류‑전압 특성을 파라메트릭 형태로 근사함으로써 수백 개의 샘플에 대해 수밀리초 수준의 계산을 가능하게 한다. 둘째, 공정 파라미터와 회로 설계 파라미터를 동시에 최적화하는 다목적 탐색 알고리즘(예: 베이지안 최적화 + 진화적 전략)을 적용한다. 탐색 과정에서 ‘수율(금속성 CNT 제거율·밀도 균일성)’, ‘노이즈 마진(전압 스윙·임계 전압 변동)’, ‘에너지·지연’이라는 세 가지 목표를 명시적으로 고려한다.

실험 결과는 두드러진 세 가지 인사이트를 제공한다. ① 금속성 CNT 제거율이 99.9% 이상이어야 전체 수율이 99% 수준을 유지할 수 있으며, 이는 공정 단계에서 선택적 화학적 제거(예: 전기적 절단) 기술의 중요성을 강조한다. ② CNT 밀도와 직경 분포는 회로 지연에 가장 큰 영향을 미치며, 목표 밀도를 30 CNT/µm 정도로 설정하고 직경 변동을 ±5% 이내로 제한하면 지연 감소 효과가 최대화된다. ③ 회로 설계 측면에서는 임계 전압 변동을 보정하기 위한 트랜지스터 폭 확대와, 중요한 경로에 대한 중복 배치(리던던시) 전략이 노이즈 마진을 0.2 V 이상 확보하면서도 에너지 오버헤드를 5% 이하로 제한한다는 점을 확인한다.

특히, 제안된 프레임워크는 기존의 전통적 시뮬레이션 대비 100배 이상 빠른 평가 속도를 보이며, 설계자들이 수백 개의 공정‑회로 조합을 실시간에 가깝게 탐색할 수 있게 한다. 이는 설계 주기 단축과 함께, 공정 개발 단계에서 빠른 피드백을 제공해 제조 비용 절감에도 기여한다.

전반적으로 이 논문은 “공정 파라미터와 회로 설계 파라미터를 동시에 고려한 공동 최적화”라는 새로운 패러다임을 제시함으로써, CNT 변동이 초미세 공정에서 야기하는 실질적 장애물을 체계적으로 극복할 수 있는 로드맵을 제공한다.