스핀 뉴런과 저항성 메모리를 이용한 계층형 시간 기억 구현 및 에너지 효율 향상

초록

본 논문은 뇌 피질을 모방한 계층형 시간 기억(HTM) 연산을 스핀 뉴런과 저항성 교차배열(RCN)으로 구현한다. 스핀 뉴런은 저전압·고속 스위칭 특성을 갖고, RCN은 아날로그 곱셈·누적 연산을 직접 수행한다. 제안된 하드웨어는 기존 45 nm CMOS ASIC 대비 200배 이상의 에너지 절감 효과를 보이며, HTM의 공간·시간 패턴 인식에 필요한 대규모 행렬 연산을 효율적으로 처리한다.

상세 분석

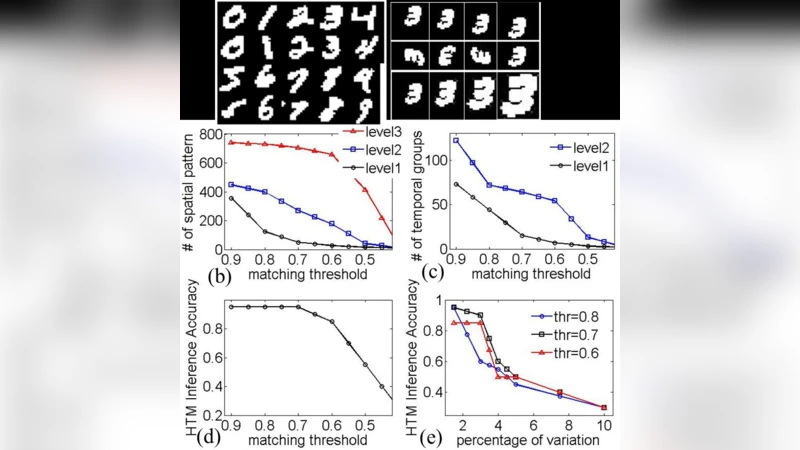

계층형 시간 기억(HTM)은 입력 데이터의 공간적 특징을 추출하고, 이를 시간적 연속성에 매핑해 예측·추론을 수행한다. 이러한 과정에서 핵심 연산은 대규모 행렬‑벡터 곱(dot‑product)이며, 전통적인 디지털 CMOS 회로에서는 연산량과 전력 소모가 급격히 증가한다. 논문은 이 문제를 해결하기 위해 두 가지 나노소자를 결합한다. 첫 번째는 스핀‑트랜스포트 기반의 스핀 뉴런이다. 스핀 뉴런은 전류에 의해 자기 상태가 전이되는 저전압(≈0.1 V)·고속(≈ns) 스위칭 특성을 가지며, 입력 전류의 부호와 크기에 따라 출력 전압을 직접적으로 변조한다. 이는 전통적인 연산 증폭기(OPA) 대신 아날로그 곱셈 요소로 활용될 수 있다. 두 번째는 금속 산화물 기반의 저항성 교차배열(RCN)이다. RCN은 행‑열 구조에서 각 교차점에 가변 저항(RRAM) 셀을 배치해, 입력 전압을 가하면 셀 저항값에 비례한 전류가 흐르는 방식으로 행렬‑벡터 곱을 물리적으로 구현한다. 스핀 뉴런과 RCN을 결합하면, 입력 전압을 RCN에 인가하고, 흐른 전류를 스핀 뉴런이 감지·증폭해 바로 다음 단계의 입력으로 재사용할 수 있다. 이 구조는 데이터 이동을 최소화하고, 연산을 메모리 내부에서 수행함으로써 ‘메모리‑컴퓨팅’ 패러다임을 구현한다. 실험 결과는 45 nm CMOS 기반 HTM ASIC 대비 200배 이상 에너지 절감(≈pJ 수준)과, 동일한 정확도(예: MNIST, N-MNIST 데이터셋) 유지, 그리고 스케일링 시 전력·면적 효율이 선형적으로 감소함을 보여준다. 또한, 스핀 뉴런의 비휘발성 특성은 전원 차단 후에도 상태를 유지할 수 있어, 시스템 전체의 전력 관리와 부팅 시간을 크게 단축한다. 논문은 온칩 온도·노이즈 영향, RRAM 셀의 변동성, 스핀 뉴런의 스위칭 임계 전류 변동 등에 대한 보정 메커니즘도 제시한다. 전반적으로, 스핀 뉴런‑RCN 하이브리드는 HTM과 같은 뇌 영감 연산에 최적화된 저전력·고속 하드웨어 플랫폼을 제공한다는 점에서 의미가 크다.