아날로그 비휘발성 메모리를 활용한 뉴로모픽 설계 핵심 고려사항

초록

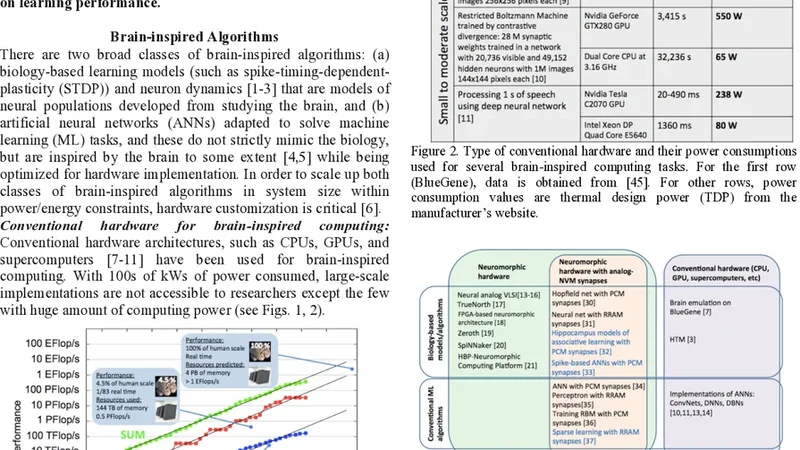

본 논문은 아날로그 비휘발성 메모리(NVM)를 전자 시냅스로 이용한 뉴로모픽 시스템의 최신 동향을 정리하고, 멀티레벨 상태 구현, 디바이스 변동성, 프로그래밍 에너지, 배열 연결성, 팬인/팬아웃, 배선 전력 및 IR 드롭 등 설계 단계별 주요 과제와 해결 방안을 제시한다. 특히 대규모 시스템에서 배선 에너지와 사이클 간 변동이 학습 성능에 미치는 영향을 강조한다.

상세 분석

논문은 아날로그 NVM(주로 RRAM, PCM, MRAM 등)이 전통적인 디지털 메모리와 달리 연속적인 전도값을 제공함으로써 가중치의 멀티레벨 저장이 가능하다는 점을 출발점으로 삼는다. 이러한 멀티레벨 특성은 신경망의 정밀도와 학습 효율을 크게 향상시킬 수 있지만, 실제 디바이스에서는 상태 간 간격이 비선형이고, 온도·공정 변동에 따라 큰 변동성을 보인다. 저자는 변동성을 두 가지 차원—디바이스 간 정적 변동(공정 편차)과 사이클 간 동적 변동(프로그래밍 노이즈)—으로 구분하고, 각각이 가중치 업데이트 정확도와 수렴 속도에 미치는 영향을 정량적으로 분석한다. 특히, 사이클 간 변동이 10 % 수준을 초과하면 학습 초기에 급격한 손실 증가가 발생하며, 이를 완화하기 위해 적응형 학습률 조정이나 오류 보정 회로가 필요함을 제시한다.

프로그래밍 에너지 측면에서는 전압 펄스 폭과 전류 제한을 최적화함으로써 10 nJ 이하의 에너지로 1 bit 업데이트가 가능하다는 실험 결과를 인용한다. 그러나 멀티레벨 저장을 위해서는 더 정밀한 전압 제어가 요구되며, 이 경우 에너지 소모가 비선형적으로 증가한다. 따라서 설계자는 에너지·정밀도 트레이드오프를 명확히 정의하고, 애플리케이션 요구에 따라 최소 4‑bit 수준의 멀티레벨을 목표로 하는 것이 현실적이라고 주장한다.

배열 수준에서는 팬인/팬아웃 제한이 핵심 이슈다. 한 셀에 연결 가능한 입력 수가 증가하면 라인 저항과 정전용량이 커져 신호 감쇠와 타이밍 지연이 발생한다. 저자는 64 × 64 규모의 크로스바 배열을 기준으로, 최대 128개의 팬인을 허용하려면 라인당 저항을 1 Ω 이하로 유지하고, 배선 길이를 10 µm 이하로 제한해야 한다고 제시한다. 또한, 배선 자체가 차지하는 에너지(와이어 에너지)가 전체 시스템 에너지의 30 % 이상을 차지할 수 있음을 강조한다. 이때 IR 드롭이 가중치 읽기·쓰기 정확도에 미치는 영향을 최소화하기 위해, 전압 레벨 보정 회로와 분산 전원 공급 방식을 병행하는 것이 필요하다.

시스템 통합 관점에서는 디바이스 레벨의 변동성을 알고리즘 수준에서 보완하는 방법과, 회로 설계 단계에서 변동성을 최소화하는 물리적 설계(예: 온도 제어, 균일한 전류 분배) 사이의 협업이 중요하다고 강조한다. 특히, 대규모 뉴로모픽 시스템에서는 배선 설계와 전원 관리가 전체 성능과 에너지 효율을 좌우하므로, 전통적인 메모리 설계와는 다른 새로운 설계 패러다임이 요구된다.