실리콘 초박막 트랜지스터를 위한 범용 암시적 패시베이션 방법

초록

본 논문은 기존 경험적 타이트 바인딩(TB) 모델의 한계를 극복하고, 임의의 패시베이션 시나리오에 적용 가능한 새로운 암시적 패시베이션 기법을 제안한다. Si 양자우물과 Si 초박막(UTB) 트랜지스터의 SiO₂ 산화 구조에 적용해 ab‑initio 계산 및 실험과 비교함으로써 모델의 정확성을 검증하고, 특정 산화 구성에서 트랜지스터 성능이 크게 저하되는 메커니즘을 규명한다. 또한, 전통적인 암시적 H 패시베이션이 실제 성능을 과대평가함을 보여준다.

상세 분석

이 연구는 경험적 타이트 바인딩(Empirical Tight Binding, TB) 모델에서 결함이 되는 다이앵글링 결합을 어떻게 효과적으로 패시베이션할 것인가에 대한 근본적인 문제를 다룬다. 기존 방법은 크게 두 가지로 나뉜다. 첫 번째는 실제 패시베이션 원자를 모델에 명시적으로 포함시키는 방식으로, 이는 H, O 등 단일 원자 혹은 작은 분자에만 적용 가능하고, 원자 수가 늘어나면 계산 비용이 급증한다. 두 번째는 패시베이션 효과를 매개변수화된 전위 혹은 에너지 레벨 변형으로 암시적으로 구현하는 방식인데, 이 경우 패시베이션 원자의 종류와 화학적 특성을 구분하지 못해 물리적 정확도가 떨어진다. 논문은 이러한 한계를 극복하기 위해, 패시베이션 원자의 전자 구조와 결합 특성을 반영한 새로운 암시적 매개변수 세트를 도입한다. 구체적으로, 각 패시베이션 원자(예: H, O, Si‑O‑Si 등)에 대해 온사이트 에너지와 홉 파라미터를 별도로 정의하고, 이들을 기존 TB 해밀리안에 추가함으로써 원자 수준의 전자적 영향을 재현한다.

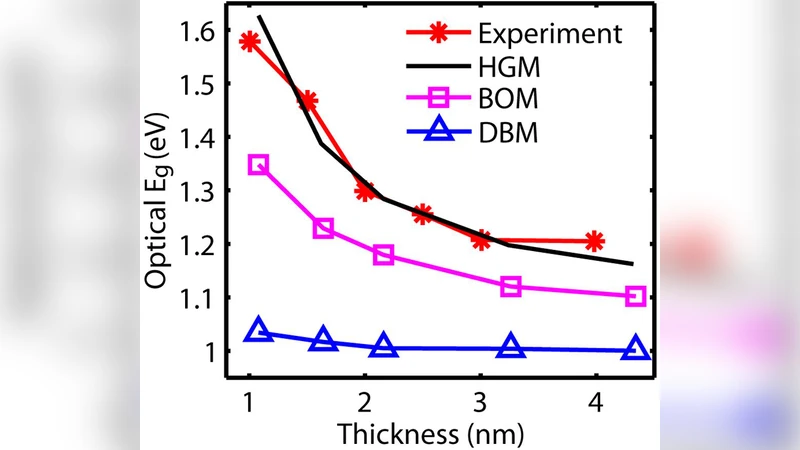

제안된 방법의 핵심은 “패시베이션 원자 유형별 파라미터화”와 “다중 결합 환경에 대한 가변 홉”이다. 이를 위해 저자들은 먼저 DFT‑G0W0 계산을 통해 다양한 Si‑O 결합 구조의 밴드 구조와 전자 친화도를 추출하고, 이를 최소 제곱법으로 TB 파라미터에 매핑한다. 이렇게 얻어진 파라미터는 Si 양자우물(QW)과 초박막(UTB) 트랜지스터의 산화층에 적용될 때, 표면 상태가 완전히 억제되고 밴드갭이 실험값과 일치하도록 보장한다.

시뮬레이션 결과는 두 가지 중요한 인사이트를 제공한다. 첫째, SiO₂ 산화가 진행될 때 Si‑O‑Si 다리 구조가 형성되면 전도대와 가전자대 사이에 새로운 트랩 레벨이 나타나 전하 이동성을 크게 저하시킨다. 둘째, 전통적인 암시적 H 패시베이션은 이러한 트랩 레벨을 무시하고, 실제보다 높은 전류와 낮은 서브스레시홀드 스윙을 예측한다. 따라서 설계 단계에서 H 패시베이션만을 가정하면 장치 최적화가 잘못된 방향으로 진행될 위험이 있다.

이와 같이, 제안된 암시적 패시베이션 모델은 원자 종류와 결합 환경을 정밀히 반영하면서도 계산 비용을 크게 증가시키지 않는다. 이는 대규모 원자 규모 시뮬레이션, 특히 3차원 나노구조와 복합 산화층을 포함한 최신 반도체 디바이스 설계에 매우 유용하다. 향후 이 방법을 다른 반도체(Ge, III‑V)와 다양한 패시베이션 화학(질소, 플루오린)에도 확장할 수 있을 것으로 기대된다.