이중 임계값을 이용한 저지연 리스트 디코딩

초록

본 논문은 폴라 코드 리스트 디코딩에서 기존의 정렬 기반 리스트 프루닝이 초래하는 높은 지연을 극복하기 위해, 두 개의 임계값을 활용하는 ‘이중 임계값 전략(DTS)’을 제안한다. DTS는 비교 연산만으로 리스트 크기 L에 대해 L개의 최적 경로를 빠르게 선택하도록 설계되었으며, 이를 위한 임계값 추적 회로와 전체 디코더 아키텍처를 90 nm CMOS 공정으로 구현하였다. 실험 결과, 리스트 크기 16에서도 641 MHz 동작 시 220 Mbps의 처리량을 달성하면서 기존 정렬 기반 설계 대비 지연을 크게 감소시켰다.

상세 분석

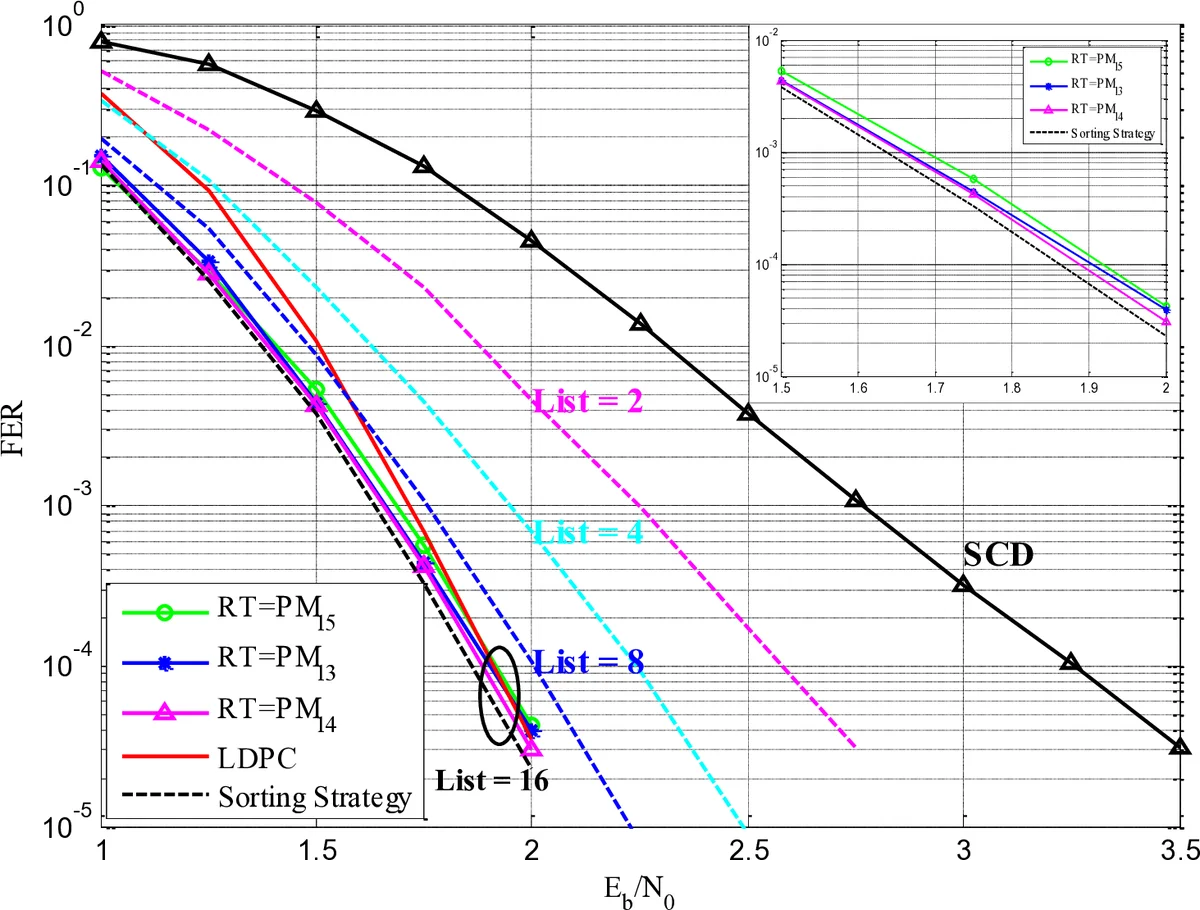

폴라 코드의 리스트 성공적 연속 취소 디코딩(L‑SCD)은 높은 오류 정정 성능을 제공하지만, 리스트 크기가 커질수록 후보 경로를 정렬하고 상위 L개를 선택하는 과정이 병목이 된다. 기존의 비트닉 정렬망이나 병렬 정렬 회로는 O(L²) 수준의 하드웨어 복잡도와 L에 비례하는 클럭 지연을 초래한다. 논문은 이러한 문제를 해결하기 위해 두 개의 임계값, 즉 Acceptance Threshold(AT)와 Rejection Threshold(RT)를 정의하고, 2L개의 확장 경로 메트릭 중 AT보다 작으면 무조건 유지, RT보다 크면 무조건 제외하고, AT와 RT 사이에 위치한 경로는 랜덤하게 선택해 리스트 크기를 맞춘다. 핵심 이론적 근거는 Proposition 1으로, 정렬된 메트릭 집합에 대해 AT=pm_{L/2}와 RT=pm_{L‑1}을 사용하면 최소 L/2개의 최적 경로가 반드시 보존되고, 최대 L개의 경로만이 선택될 수 있음을 보인다.

하드웨어 구현 측면에서 DTS는 4개의 비교기와 우선순위 인코더만으로 구현 가능하므로, 정렬 기반 설계에 비해 논리 지연이 크게 감소한다. 또한, AT와 RT를 실시간으로 업데이트하기 위한 Threshold Tracking Architecture(TTA)를 제안한다. TTA는 입력 메트릭을 두 그룹으로 나누어 각각 라디칼 정렬기를 사용하고, 단계별 MUX와 비교기를 통해 중간값(AT)과 최대값(RT)을 순차적으로 추출한다. 이 과정은 로그₂L 단계로 구성되어 전체 복잡도는 O(L·log L) 수준이며, 여러 클럭 사이클에 걸쳐 수행될 수 있어 리스트 프루닝 단계와 겹쳐 파이프라인이 가능하다.

전체 디코더 아키텍처는 L개의 SCD 유닛을 병렬로 배치하고, 각 유닛은 반병렬(semiparallel) 방식으로 M(<N/2)개의 처리 요소(PE)를 사용한다. PMU는 L개의 기존 메트릭과 새로 생성된 LLR을 이용해 2L개의 메트릭을 계산하고, 바로 DTS에 전달한다. DTS와 Lazy Copy(LCP) 블록이 동시에 동작하여 메모리 복사를 최소화하고, 최종적으로 CRC 검증을 통해 올바른 코드워드를 선택한다.

시뮬레이션 및 합성 결과, 리스트 크기 16인 경우에도 전체 디코딩 지연이 리스트 크기 8인 기존 설계보다 짧으며, 641 MHz 클럭에서 220 Mbps의 처리량을 달성한다. 성능 면에서는 CRC‑보조 리스트 디코딩과 비교했을 때 약 0.1 dB 수준의 FER 손실만을 보이며, 이는 DTS의 랜덤 선택 단계에서 발생하는 미세한 손실에 기인한다. 전체적으로, 제안된 이중 임계값 전략은 하드웨어 복잡도와 지연을 크게 낮추면서도 실용적인 오류 정정 성능을 유지하는 효과적인 솔루션이다.

댓글 및 학술 토론

Loading comments...

의견 남기기