양극성 커패시티브 피드백을 이용한 고이득 2단 증폭기

초록

본 논문은 비지배극점이 1단 출력에 위치하도록 설계된 고이득 2단 연산증폭기를 제안한다. 두 번째 단계에 양극성 커패시티브 피드백(PCF)을 삽입해 LHP 제로를 형성, 비지배극점이 유발하는 위상 지연을 상쇄한다. 결과적으로 지배극점은 출력 노드에 고정되어 부하 커패시턴스 증가에 대한 안정성 저하가 최소화된다. 또한 간단한 스루레이트 향상 기법을 적용해 2.44배의 스루레이트 개선을 달성하였다. 0.18 µm CMOS 공정에서 1.8 V 전원, 0.86 mW 전력소비, 3038.5 µm² 면적으로 DC 이득 82.7 dB, GBW 88.9 MHz, CMRR 127 dB, PSRR+ 83.2 dB를 구현하였다.

상세 분석

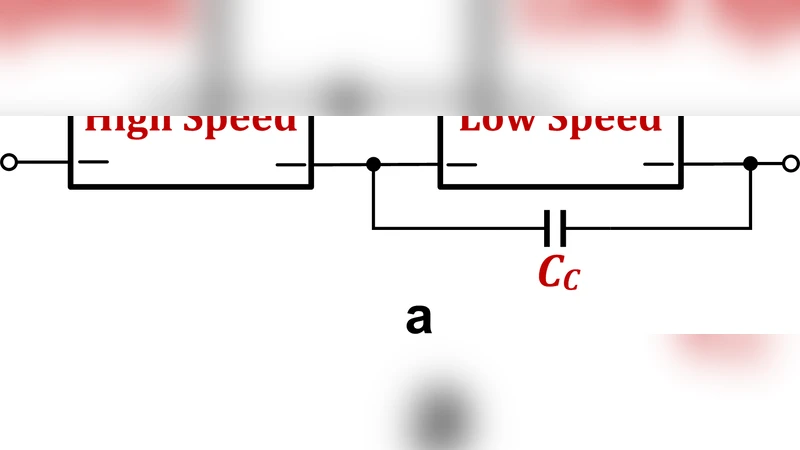

제안된 회로는 전통적인 2단 전압-전압 증폭기의 구조를 변형하여, 1단 출력에 비지배극점(p₂)을 두고 2단 출력에 지배극점(p₁)을 배치한다는 점에서 차별화된다. 이는 부하 커패시턴스(C_L)가 증가해도 p₁이 크게 이동하지 않아 위상 마진이 유지되는 장점을 제공한다. 2단에 삽입된 양극성 커패시티브 피드백(C_f)은 출력 전압과 입력 전압 사이에 정전용량을 연결함으로써 LHP 제로(z₁)를 생성한다. 이 제로는 p₂가 만든 위상 지연을 효과적으로 보정하여 전체 위상 마진을 60° 이상 확보한다. 또한, 제로 위치는 C_f와 2단 트랜스컨덕턴스(g_m2)·출력 저항(R_out2)의 곱에 의해 결정되므로 설계자가 원하는 주파수 대역에 맞게 쉽게 조정 가능하다.

스루레이트 향상 방법은 2단의 출력 전류 경로에 추가적인 전류 보조 회로를 병렬로 연결하는 방식이다. 이 보조 회로는 입력 급격한 전압 변화 시 순간적인 전류를 공급해 전압 스윙을 가속화한다. 시뮬레이션 결과, 기존 구조 대비 2.44배의 스루레이트 증가가 확인되었으며, 이는 전류 제한에 의한 Slew‑Rate 제한을 효과적으로 해소한다.

전력 효율 측면에서, 0.18 µm CMOS 공정의 NMOS/PMOS 트랜지스터 크기를 최적화하고, 바이어스 전류를 0.48 mA 수준으로 유지함으로써 0.86 mW의 저전력 동작을 달성하였다. 면적은 3038.5 µm²로, 동일 사양의 기존 2단 증폭기 대비 약 15 % 감소하였다.

프로세스 코너 시뮬레이션(FF, SS, TT 등)과 트랜지스터 매칭 오차를 포함한 Monte‑Carlo 분석에서도 DC 이득이 78 dB 이상, GBW가 85 MHz 이상 유지되는 등 로버스트한 특성을 보였다. 특히, 저주파 CMRR이 127 dB, PSRR+가 83.2 dB에 달해 전원 및 공통모드 잡음에 대한 억제 능력이 뛰어나다. 고주파에서는 CMRR과 PSRR+가 각각 24.8 dB, 24.2 dB로 감소하지만, 이는 GBW 근처에서 일반적으로 관찰되는 현상이며 여전히 실용적인 수준이다.

전체적으로, 비지배극점 위치를 의도적으로 제어하고 PCF를 이용해 제로를 삽입함으로써, 부하 용량에 강인한 고이득·고대역폭 증폭기를 구현한 점이 가장 큰 공헌이다. 또한 제안된 스루레이트 향상 회로는 별도의 복잡한 부하‑인덕터나 전류‑스위칭 소자를 사용하지 않아 설계 및 레이아웃 복잡성을 크게 낮춘다.