HfOx 기반 저항성 메모리의 변동성 및 비트 오류율 인라인 테스트

초록

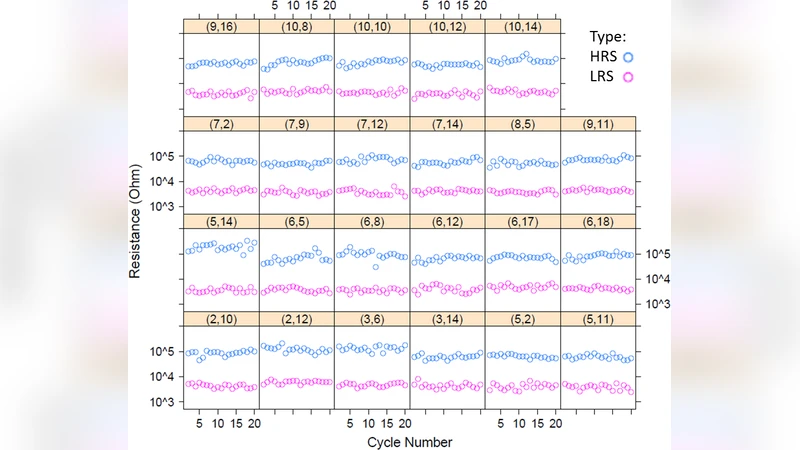

본 논문은 HfOx 소재를 이용한 저항성 랜덤 액세스 메모리(RRAM)의 제조 공정 및 사용 중 발생하는 공간·시간 변동성을 인라인 전기 테스트 데이터를 통해 정량화한다. 로트·웨이퍼·칩 수준의 변동성을 구분하여 분석하고, 쓰기 사이클에서 측정된 저항값 분포를 기반으로 설계 마진에 따른 비트 오류율(BER)을 계산하는 방법을 제시한다. 제안된 BER 모델은 설계 단계에서 기술 평가와 오류 정정 전략을 수립하는 데 활용될 수 있으며, 오프라인 벤치 테스트 및 BIST 환경에서도 적용 가능함을 보인다.

상세 분석

본 연구는 HfOx 기반 RRAM의 변동성을 다층적인 제조 단계별로 정밀히 분해한다는 점에서 의미가 크다. 로트 간 변동은 공정 파라미터의 장기적 드리프트를 반영하고, 웨이퍼 간 변동은 동일 로트 내에서도 온도·압력·플라즈마 균일성 차이에 기인한다. 칩 수준의 변동은 미세구조적 결함, 전극 접촉 저항, 그리고 산화막 두께의 미세한 차이까지 포함한다. 이러한 계층적 변동을 통계적으로 모델링함으로써, 설계자는 특정 마진을 설정했을 때 기대할 수 있는 BER을 사전에 예측할 수 있다.

특히 저항값의 로그 정규분포를 가정하고, LRS(저저항 상태)와 HRS(고저항 상태)의 평균·표준편차를 각각 추정한 뒤, 설계 마진 M을 정의한다. M은 LRS 평균과 HRS 평균 사이의 안전 구간을 의미하며, M이 클수록 오류 가능성은 감소한다. 저항값이 M을 초과하거나 미만일 경우 오류가 발생한다고 가정하고, 누적분포함수(CDF)를 이용해 각각의 오류 확률을 계산한다. 최종 BER은 두 오류 확률의 합으로 정의된다.

이 방법의 장점은 인라인 테스트 단계에서 이미 수집된 사이클 데이터만으로 BER을 추정할 수 있다는 점이다. 따라서 제조 라인에서 실시간으로 공정 변동을 모니터링하고, 필요 시 공정 파라미터를 조정하거나 오류 정정 코드를 동적으로 적용할 수 있다. 또한, 오프라인 벤치 테스트나 BIST 환경에서도 동일한 통계 모델을 적용해 메모리 셀의 신뢰성을 평가할 수 있다.

제안된 BER 모델은 기존의 단순한 오류율 측정 방식과 달리 설계 마진이라는 설계 변수와 직접 연결되므로, 설계자는 목표 BER을 달성하기 위한 마진 설정을 정량적으로 최적화할 수 있다. 이는 특히 고밀도 3D RRAM 구조에서 전압·전류 변동이 심해지는 상황에서 유용하다.

마지막으로, 논문은 실험 결과를 통해 로트·웨이퍼·칩 수준의 변동이 각각 BER에 미치는 영향을 정량적으로 제시한다. 로트 간 변동이 가장 큰 영향을 미치며, 웨이퍼와 칩 수준 변동은 상대적으로 작지만 누적 효과를 무시할 수 없다는 결론을 도출한다. 이러한 통합적인 변동·BER 분석 프레임워크는 향후 HfOx 기반 메모리뿐만 아니라 다른 종류의 RRAM 및 비휘발성 메모리 기술에도 확장 적용 가능성을 시사한다.

댓글 및 학술 토론

Loading comments...

의견 남기기