FPGA 가속기 설계를 위한 OpenCL 2.0 활용 – OCLAcc 완전 분석

초록

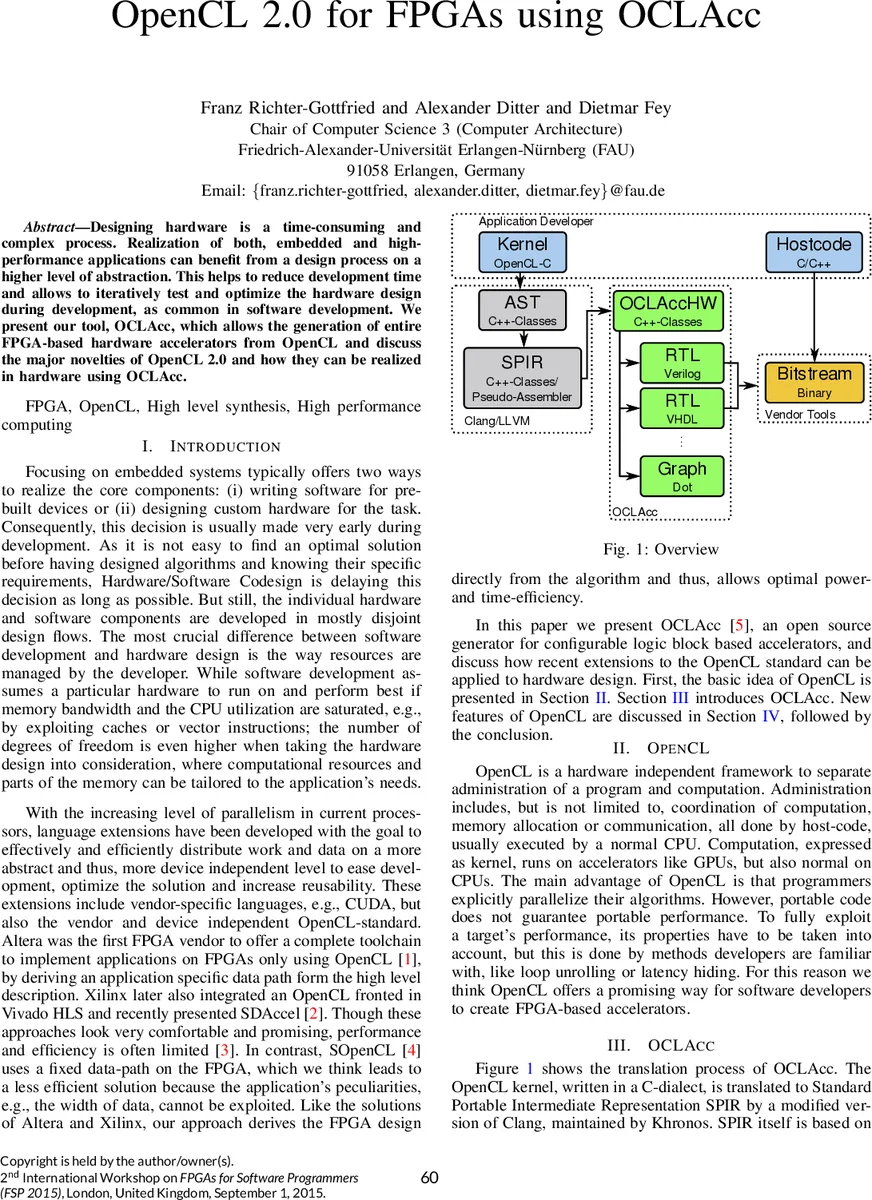

본 논문은 OpenCL 2.0 기반 FPGA 가속기 생성 도구 OCLAcc의 설계와 구현을 소개한다. OpenCL 커널을 SPIR로 변환하고, 내부 데이터 흐름 표현(OCLAccHW)으로 매핑한 뒤, 벤더 툴을 이용해 RTL/IP를 자동 생성한다. 특히 워크‑그룹 함수, 파이프, 디바이스‑사이드 엔큐, 공유 가상 메모리(SVM) 등 OpenCL 2.0 신규 기능을 하드웨어에 어떻게 구현할 수 있는지를 상세히 논의한다.

상세 분석

OCLAcc는 OpenCL 1.2와 SPIR 2.0을 기반으로 하면서도 OpenCL 2.0의 핵심 확장 기능을 FPGA 설계에 적용하려는 시도를 보여준다. 첫 번째 단계에서는 수정된 Clang이 OpenCL‑C 커널을 SPIR 바이너리로 변환하고, 이를 LLVM‑VM‑IR에 통합한다. 두 번째 단계인 OCLAccHW 생성에서는 커널을 기본 블록(basic block) 단위로 분할하고, 각 블록의 입출력 스트림을 분석해 메모리 인덱스를 정적·동적으로 파악한다. 이 과정에서 OpenCL 표준이 요구하는 내장 함수(예: barrier, atomic 등)를 전용 하드웨어 컴포넌트와 제어 신호에 매핑한다. 또한 공통 부분식 제거와 같은 하드웨어‑특화 최적화가 수행된다. HWMap 단계에서는 벤더‑특정 툴체인(Altera, Xilinx 등)을 호출해 IP‑코어를 직접 인스턴스화하거나, 자동 추론에 맡긴다. 여기서 중요한 점은 클럭‑드리븐 동기화가 기본 블록 내부에서만 적용되고, 블록 간에는 ready/ack 프로토콜을 사용한다는 것이다. 이는 실제 FPGA 구현 시 타이밍 정보를 사전에 알 수 없는 경우에도 안정적인 파이프라인 구성을 가능하게 한다. OpenCL 2.0의 워크‑그룹 함수는 로컬 SRAM에 데이터를 저장하고, 모든 워크‑아이템이 도달할 때까지 대기한 뒤 연산을 수행하도록 구현된다. 파이프는 호스트가 정의한 FIFO 깊이와 차원을 SRAM 기반 버퍼로 구현해, 커널 간 데이터 흐름을 자동화한다. 디바이스‑사이드 엔큐는 동적으로 생성된 커널을 실행하기 위한 워크‑큐를 FPGA 내부 FIFO로 구현함으로써 호스트와의 왕복 오버헤드를 제거한다. 마지막으로 SVM은 현재 coarse‑grained만 지원하며, 포인터 매핑·언매핑 메커니즘을 통해 호스트와 디바이스가 동일 주소 공간을 공유하도록 설계되었다. OCLAcc는 이러한 기능들을 오픈소스로 제공함으로써, 기존 Altera·Xilinx 솔루션이 갖는 고정 데이터패스나 성능 제한을 극복하고, 설계자에게 더 큰 자유도와 최적화 여지를 제공한다. 다만 OpenCL 2.0 전체 표준을 완전 구현하지는 않으며, fine‑grained SVM 등 일부 고급 기능은 향후 과제로 남아 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기