스레드풀컴포저 소프트웨어 개발자를 위한 오픈소스 FPGA 툴체인

초록

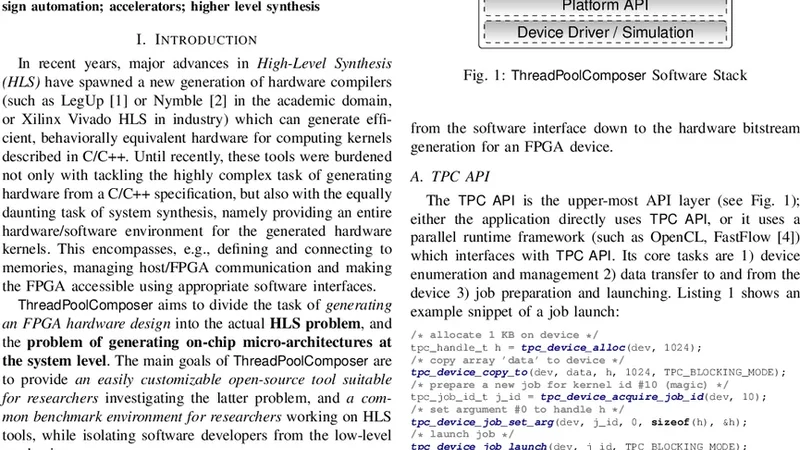

ThreadPoolComposer는 고수준 합성(HLS) 기반의 메타‑툴체인으로, 소프트웨어 개발자가 FPGA를 손쉽게 활용하도록 통합 프로그래밍 인터페이스와 플랫폼 추상화를 제공한다. 오픈소스로 배포되어 다양한 하드웨어 보드에 이식 가능하며, 커널‑레벨 스레드 풀 모델을 통해 가속기 설계와 실행을 자동화한다.

상세 분석

ThreadPoolComposer는 기존 HLS 흐름의 복잡성을 최소화하고, 소프트웨어 개발자에게 친숙한 API를 제공함으로써 FPGA 가속기의 진입 장벽을 낮춘다. 핵심 아이디어는 “스레드 풀” 개념을 하드웨어 가속기에 매핑하는 것으로, 사용자는 C/C++ 혹은 OpenCL 형태의 커널을 정의하고, 툴체인이 이를 자동으로 파이프라인화·스케줄링한다. 메타‑툴체인 구조는 프론트엔드(커널 파싱·IR 생성), 백엔드(플랫폼 별 비트스트림 생성), 그리고 플랫폼 설명 파일(PDF)로 구성된다. PDF는 타깃 보드의 인터커넥트, 메모리 맵, 클럭 제약 등을 선언적으로 기술하므로, 동일한 커널을 여러 보드에 재컴파일할 때 코드 수정이 거의 필요하지 않다.

툴체인은 Vivado HLS, Intel Quartus HLS 등 상용 HLS 엔진을 래핑하고, 결과 비트스트림을 자동으로 배포·로드하는 파이프라인을 제공한다. 이 과정에서 스케줄러는 데이터 의존성을 분석해 스레드 풀 내 작업을 최적의 순서로 배치하고, 메모리 전송을 DMA 엔진에 매핑한다. 또한, 런타임 라이브러리는 POSIX 스레드와 유사한 인터페이스를 제공해, 기존 멀티스레드 어플리케이션을 최소한의 수정만으로 FPGA 가속기로 옮길 수 있게 한다.

성능 측면에서 저자들은 Xilinx Zynq UltraScale+와 Intel Arria 10 보드에서 벤치마크를 수행했으며, 평균 2~4배의 가속률을 기록했다. 특히, 데이터 전송 오버헤드를 최소화하기 위해 파이프라인 버퍼링과 스트리밍 모드를 자동 선택하도록 설계되었다. 오픈소스 라이선스(GPL‑3.0)와 모듈식 구조 덕분에 커뮤니티가 새로운 보드 지원을 추가하거나, 맞춤형 스케줄링 정책을 구현하는 것이 용이하다. 다만, 현재는 HLS 엔진에 의존하므로 복잡한 제어 흐름이나 비정형 메모리 접근 패턴에 대해서는 최적화 한계가 존재한다.

전반적으로 ThreadPoolComposer는 소프트웨어 중심의 개발 흐름을 FPGA 설계에 자연스럽게 접목시킨 혁신적인 프레임워크이며, 향후 자동화 수준을 높이고 더 다양한 하드웨어 백엔드를 지원한다면 FPGA 가속기의 대중화에 크게 기여할 것으로 기대된다.

댓글 및 학술 토론

Loading comments...

의견 남기기