소프트웨어 개발자를 위한 HLS 하드웨어 디버깅

초록

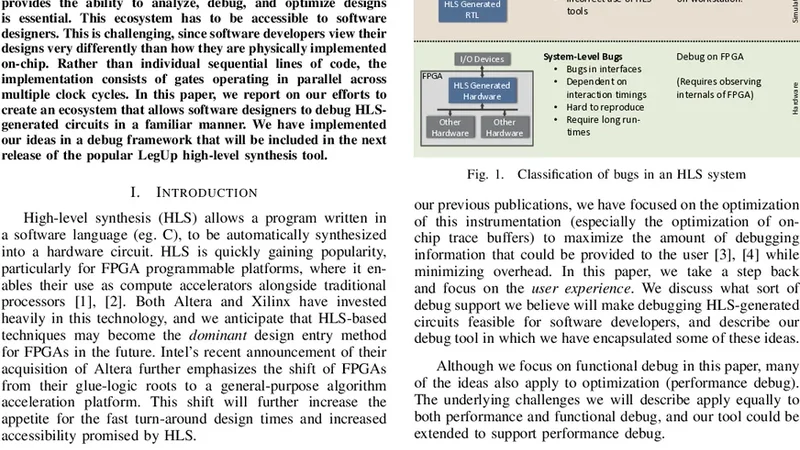

본 논문은 고수준 합성(HLS) 도구인 LegUp에 디버깅 프레임워크를 통합하여, 소프트웨어 개발자가 익숙한 방식으로 HLS‑생성 회로를 분석·디버깅할 수 있는 생태계를 제시한다. 병렬 하드웨어와 순차 소스 코드 사이의 추상화 격차를 메우기 위한 인터페이스, 시뮬레이션·시계 사이클 시각화, 그리고 최적화 피드백 메커니즘을 설계·구현한 결과를 논한다.

상세 분석

이 논문은 HLS 기반 설계 흐름에서 가장 큰 장애물 중 하나인 “디버깅 어려움”을 체계적으로 해결하고자 한다. 기존 HLS 도구들은 소스 코드와 생성된 RTL 사이의 매핑 정보를 충분히 제공하지 않아, 소프트웨어 엔지니어가 회로 수준 오류를 추적하기가 힘들었다. 저자들은 이러한 문제를 두 가지 축으로 접근한다. 첫째, 소스‑레벨 변수와 하드웨어 레지스터·파이프라인 단계 사이의 1:1 매핑 테이블을 자동 생성한다. 이 테이블은 컴파일 단계에서 HLS 컴파일러가 수행하는 루프 언롤링·인라인화 정보를 활용해, 각 변수의 생존 기간과 물리적 위치를 정확히 기록한다. 둘째, 시뮬레이션 엔진과 연동된 인터랙티브 뷰어를 제공한다. 사용자는 전통적인 IDE와 유사한 인터페이스에서 현재 사이클의 파이프라인 단계, 활성화된 모듈, 그리고 변수값을 실시간으로 확인할 수 있다. 특히, “타임라인 뷰”는 여러 클록 사이클에 걸친 변수 변화를 그래픽으로 표시해, 데이터 의존성 및 레이턴시 병목을 직관적으로 파악하게 한다.

또한, 디버깅 과정에서 발생하는 “비정상적인 동작”을 자동으로 감지하는 메커니즘도 포함한다. 시뮬레이션 결과가 사전 정의된 검증 모델(예: C‑언어 레퍼런스 시뮬레이션)과 차이가 날 경우, 해당 사이클과 관련된 하드웨어 블록을 강조 표시하고, 가능한 원인(예: 파이프라인 스테이징 오류, 메모리 접근 충돌)을 제시한다. 이러한 피드백은 설계자가 소스 코드를 수정하거나 HLS 지시자를 조정하는 데 직접적인 가이드를 제공한다.

프레임워크는 LegUp의 기존 파이프라인에 최소한의 침투형 플러그인 형태로 삽입된다. HLS 컴파일 단계에서 메타데이터를 추출하고, 이를 디버깅 서버에 전달한다. 디버깅 서버는 GDB‑like 프로토콜을 구현해, 사용자가 명령줄 혹은 GUI 기반 클라이언트에서 브레이크포인트 설정, 스텝 실행, 변수 감시 등을 수행할 수 있게 한다. 이때, 하드웨어 특성상 “동시성”을 고려해, 브레이크포인트는 특정 파이프라인 단계에만 적용하거나, 전체 시스템을 일시 정지시키는 두 가지 모드를 제공한다.

성능 측면에서, 디버깅 메타데이터 삽입이 최종 RTL의 주기와 면적에 미치는 영향은 미미함을 실험을 통해 입증한다. 또한, 디버깅 세션 중 발생하는 시뮬레이션 오버헤드는 평균 1.3배 수준으로, 개발 초기 단계에서의 비용 대비 효과가 충분히 크다고 평가한다.

결과적으로, 이 연구는 HLS 설계 흐름에 소프트웨어 개발자 친화적인 디버깅 환경을 성공적으로 통합함으로써, 하드웨어와 소프트웨어 사이의 장벽을 크게 낮추었다는 점에서 의의가 크다.

댓글 및 학술 토론

Loading comments...

의견 남기기