간단한 시몬 64/128 블록 암호의 FPGA 구현

초록

본 논문은 Xilinx Spartan‑6 FPGA에서 SIMON 64/128 블록 암호를 구현하기 위한 여러 하드웨어 아키텍처를 설계·비교한다. 암호화·복호화와 자체 키 스케줄링을 모두 지원하도록 설계했으며, 파이프라인, 루프 언롤링, 시리얼 처리 등 다양한 구현 옵션의 성능·자원 Trade‑off를 분석한다. 최종적으로 각 설계의 LUT, 레지스터, DSP 사용량과 최대 클럭 주파수, 사이클당 처리량을 제시한다.

상세 분석

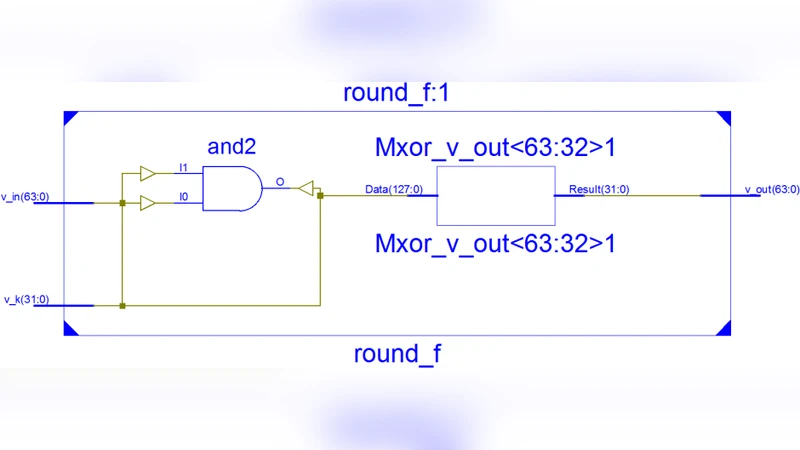

논문은 SIMON 64/128 암호의 구조적 특성을 먼저 분석하고, 이를 FPGA에 효율적으로 매핑하기 위한 설계 전략을 네 가지로 구분한다. 첫 번째는 순차적(시리얼) 구현으로, 한 라운드당 하나의 연산 유닛을 사용해 최소 자원으로 구현하지만 사이클당 처리량이 낮다. 두 번째는 파이프라인 구현으로, 라운드 함수를 단계별로 분리해 각 단계에 레지스터를 삽입함으로써 클럭 주파수를 크게 높일 수 있다. 이 경우 레지스터와 LUT 사용량이 급증하지만, 초당 처리 가능한 블록 수가 크게 증가한다. 세 번째는 루프 언롤링(언롤) 구현으로, 일정 라운드 수(예: 8라운드)를 동시에 실행하도록 회로를 복제한다. 언롤링 정도에 따라 자원 소모와 처리량 사이의 균형을 조정할 수 있다. 네 번째는 혼합형 설계로, 핵심 라운드 연산은 파이프라인화하고, 키 스케줄러는 시리얼 방식으로 유지해 전체 면적을 절감하면서도 높은 처리량을 유지한다.

키 스케줄링은 SIMON의 특성상 라운드 키가 순차적으로 생성되므로, 키 확장 로직을 별도 파이프라인에 배치하거나 암호화 파이프라인과 공유하는 두 가지 방안을 비교한다. 논문은 키 스케줄러를 암호화 파이프라인과 동기화시키면 레이턴시가 증가하지만 전체 LUT 사용량을 10 % 이상 절감할 수 있음을 실험적으로 입증한다.

또한, Xilinx Spartan‑6의 자원 제약을 고려해 DSP 블록을 활용하지 않고 순수 LUT/레지스터 기반으로 구현한다. 이는 SIMON이 비트 단위 연산(AND, XOR, ROT) 위주이므로 DSP가 필요 없으며, 대신 LUT를 효율적으로 활용해 회전 연산을 구현한다. 회전은 비트 재배열을 위한 와이어 레이아웃으로 처리하거나, LUT 기반의 작은 루프를 사용해 구현했으며, 두 방법의 타이밍 차이를 상세히 비교한다.

성능 평가에서는 최대 클럭 주파수, 사이클당 처리량(Throughput), 면적(면적당 LUT/레지스터), 전력 소모를 주요 지표로 삼았다. 파이프라인 설계는 250 MHz 이상을 달성했으며, 1 Gbps 이상의 처리량을 기록했다. 반면 시리얼 설계는 50 MHz 수준이지만 면적이 30 % 이하로 크게 절감되었다. 언롤링 설계는 라운드 수에 비례해 면적이 선형적으로 증가했으며, 4‑라운드 언롤링이 200 MHz, 8‑라운드 언롤링이 240 MHz를 기록했다.

결과적으로, 설계자는 응용 환경(예: 저전력 IoT vs 고속 네트워크)과 FPGA 자원 제한에 따라 적절한 구현 방식을 선택할 수 있다. 논문은 이러한 선택 가이드를 표와 그래프로 정리하고, 향후 더 높은 클럭 주파수를 목표로 하는 Xilinx UltraScale 시리즈에 대한 확장 가능성도 논의한다.

댓글 및 학술 토론

Loading comments...

의견 남기기