GPU 기반 실시간 트리거를 위한 초저지연 NIC NaNet

초록

**

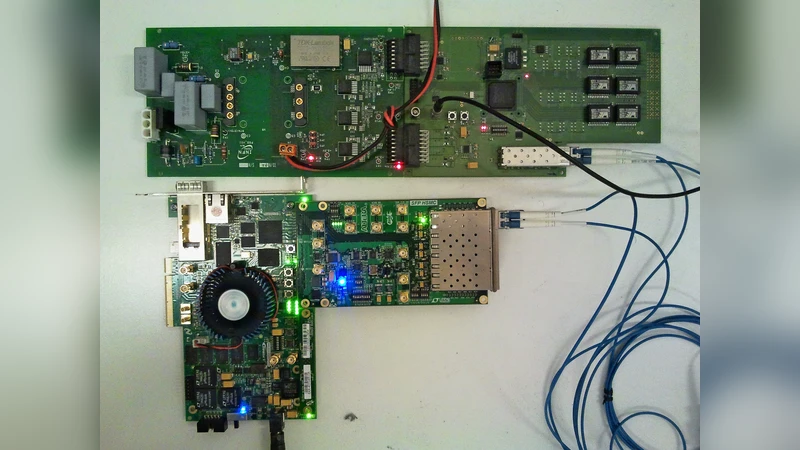

NaNet은 FPGA‑기반 PCIe Gen2 x8 인터페이스를 갖춘 NIC로, 1 GbE·10 GbE·34 Gbps APElink를 지원한다. GPUDirect RDMA와 네트워크 스택 오프로드 기능을 통해 GPU 메모리로 직접 데이터 전송이 가능해, 실시간 저지연 트리거 시스템에 최적화된 설계이다. NA62 실험 RICH 검출기의 L0 트리거 사례에서 GbE와 APElink 모두 수십 마이크로초 수준의 지연과 높은 대역폭을 입증하였다.

**

상세 분석

**

NaNet은 기존 APEnet+ 3D NIC의 핵심인 Distributed Network Processor(DNP)를 기반으로, GPU‑Direct RDMA 기능을 그대로 물려받았다. 이 기능은 PCIe 루트 복합체를 공유하는 GPU와 NIC 사이에 CPU 개입 없이 피어‑투‑피어 메모리 접근을 가능하게 하여, 데이터 전송 지연을 최소화한다. 설계는 물리링크 코딩(Physical Link Coding) 블록, UDP 오프로드(UDP Offloader), NaNet 컨트롤러, 라우터, 그리고 PCIe 인터페이스로 구성된다. 물리링크 코딩은 Altera Triple Speed Ethernet Megacore(TSE MAC)를 이용해 1 GbE를 구현하고, APElink는 8 lane QSFP+를 통해 34 Gbps 원시 전송률을 제공한다. UDP 오프로드는 Nios II 마이크로컨트롤러의 부담을 크게 줄여, 패킷 헤더/페이로드 분리를 하드웨어 수준에서 수행한다. NaNet 컨트롤러는 APEnet+ 프로토콜 헤더·풋터를 삽입해 GPU 메모리로 직접 DMA 전송을 준비하고, 라우터는 다중 채널을 동적으로 매핑한다.

성능 측정에서는 GbE 링크에서 1 KB~1 MB 크기의 버퍼에 대해 800 MB/s에 근접하는 대역폭을 유지했으며, 지연은 5 µs 이하로 안정적이었다. APElink는 구현상의 RX 경로 제한에도 불구하고 약 20 Gbps의 지속적인 전송률을 달성했고, 패킷당 추가 지연은 Nios II가 수행하는 가상‑물리 주소 변환에 의해 1.6 µs 정도였다. 이러한 지연은 전체 트리거 파이프라인(데이터 수신 → GPU 커널 처리 → 결과 전송)에서 10 µs 이하로 유지되어, NA62 L0 트리거의 실시간 요구사항을 충분히 만족한다.

향후 로드맵으로는 10 GbE 지원을 위한 NaNet‑10 개발이 진행 중이며, Stratix V FPGA와 Gen3 PCIe를 활용해 8 GB/s 양방향 전송을 목표로 한다. 또한 KM3 실험용 NaNet‑3은 8B/10B 인코딩과 TDMP 프로토콜을 사용해 deterministic latency를 보장하도록 설계되고 있다. 이러한 확장은 NaNet을 다양한 HEP 실험뿐 아니라, 저지연이 필수인 금융·통신 분야에도 적용 가능하게 만든다.

**

댓글 및 학술 토론

Loading comments...

의견 남기기