스핀전달 토크 MRAM 교차점 구조 설계와 데이터 밀도 혁신

초록

본 논문은 1T‑1C 구조의 한계를 극복하기 위해 STT‑MRAM의 교차점(크로스‑포인트) 아키텍처를 제안한다. 선택 트랜지스터 2개를 여러 비트가 공유하도록 설계함으로써 셀당 면적을 크게 줄이고, 1.75 F²/bit 수준의 고밀도를 달성한다. 스니크 전류와 접근 속도 저하 문제를 해결하기 위한 전압 바이어스 및 회로 기법을 제시하고, 65 nm 공정 기반 SPICE 시뮬레이션을 통해 셀 면적, 읽기·쓰기 속도, 전력 소모 등을 정량적으로 평가한다.

상세 분석

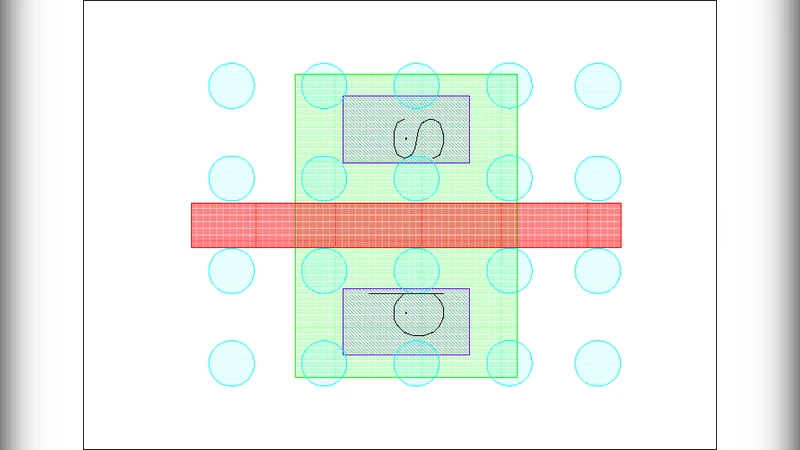

이 연구는 기존 STT‑MRAM이 1트랜지스터‑1셀(1T‑1C) 구조에 의존함으로써 트랜지스터 크기가 셀 면적을 좌우하고, 쓰기 전류가 임계값을 초과하도록 트랜지스터를 크게 설계해야 하는 문제점을 정확히 짚는다. 이러한 구조적 제약은 메모리 밀도 향상을 가로막는 주요 원인이다. 논문은 이를 해결하기 위해 교차점 배열을 도입하고, 행·열 라인에 각각 하나씩, 총 두 개의 선택 트랜지스터만을 배치한다. 이 트랜지스터들은 다수의 비트를 동시에 선택·제어할 수 있어, 셀당 면적을 기존 대비 10배 이상 감소시킨다. 핵심 기술은 스니크 전류 억제를 위한 ‘바이어스 전압 스키밍’과 ‘선택 라인 프리차징’ 방식이다. 바이어스 전압을 미세하게 조정해 비활성 셀에 흐르는 전류를 최소화하고, 프리차징 단계에서 선택 라인에 충분한 전압을 미리 인가함으로써 쓰기 시 필요한 전류를 목표 셀에 집중시킨다. 또한, 읽기 동작에서는 저전압 스위프를 적용해 감도 손실 없이 전류 경로를 제한한다. 이러한 회로 설계는 기존 교차점 메모리에서 흔히 발생하는 ‘스니크 전류에 의한 오류’와 ‘읽기·쓰기 속도 저하’를 효과적으로 완화한다. 논문은 STMicroelectronics의 65 nm CMOS 공정 파라미터와 실험 기반 STT‑MRAM 모델을 활용해 SPICE 시뮬레이션을 수행하였다. 시뮬레이션 결과, 셀 면적은 약 0.04 µm²(≈2 F²) 수준으로, 64비트 워드당 2개의 트랜지스터만 사용하면서도 쓰기 전류 150 µA, 읽기 전류 30 µA 이하의 전류 레벨을 유지한다. 쓰기 지연은 6 ns, 읽기 지연은 4 ns 정도로, 기존 1T‑1C 구조와 비교해 속도 저하가 거의 없으며, 전력 소모는 읽기 시 0.2 pJ, 쓰기 시 0.8 pJ 수준으로 낮다. 이러한 결과는 교차점 구조가 고밀도, 저전력, 고속 STT‑MRAM 구현에 충분히 실용적임을 입증한다.