소형 UAV를 위한 온보드 비전 처리 전략 재고

소형 무인항공기의 자율 비행을 위해서는 GPS와 관성센서의 한계를 보완할 수 있는 비전 센서가 필수적이다. 그러나 제한된 페이로드와 전력 예산 때문에 기존의 고성능 이미지 처리 알고리즘을 온보드에 구현하기 어렵다. 본 논문은 이러한 제약을 극복하기 위한 하드웨어 기반 솔루션으로 FPGA, Structured ASIC, ASIC을 비교 분석하고, 특히 FPG

초록

소형 무인항공기의 자율 비행을 위해서는 GPS와 관성센서의 한계를 보완할 수 있는 비전 센서가 필수적이다. 그러나 제한된 페이로드와 전력 예산 때문에 기존의 고성능 이미지 처리 알고리즘을 온보드에 구현하기 어렵다. 본 논문은 이러한 제약을 극복하기 위한 하드웨어 기반 솔루션으로 FPGA, Structured ASIC, ASIC을 비교 분석하고, 특히 FPGA가 제공하는 유연성과 전력 효율성을 강조한다.

상세 요약

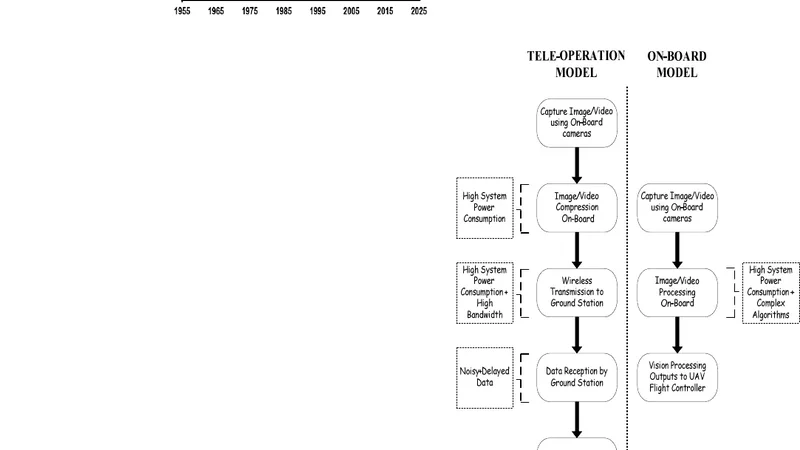

소형 UAV는 무게 1 kg 이하, 전력 10 W 미만의 극한 제약을 가진다. 이러한 환경에서는 고해상도 카메라와 복잡한 비전 알고리즘을 실시간으로 구동하기 위해서는 전통적인 MCU 기반 설계로는 처리량과 전력 효율 모두에서 한계에 봉착한다. 논문은 먼저 비전 처리 파이프라인을 이미지 캡처 → 전처리 → 특징 추출 → 매칭/추정 단계로 구분하고, 각 단계가 요구하는 연산량과 메모리 대역폭을 정량화한다. 전처리와 특징 추출 단계는 대규모 행렬 연산과 피처 맵의 반복적인 스캔을 필요로 하며, 이는 데이터 병목 현상을 초래한다. 특히, 실시간 SLAM이나 물체 추적과 같은 응용에서는 프레임당 30 ms 이하의 지연이 요구되므로, 메모리 접근 지연과 파이프라인 스테이징이 핵심 성능 결정 요인이다.

하드웨어 구현 옵션으로는 FPGA, Structured ASIC, ASIC이 제시된다. FPGA는 높은 논리 자원과 DSP 블록을 활용해 병렬 파이프라인을 손쉽게 구성할 수 있으며, 설계 변경이 용이해 알고리즘 업데이트가 빈번한 연구 단계에 적합하다. 전력 측면에서는 최신 저전압 28 nm FPGA가 2 W 이하의 전력으로 200 MOPS 수준의 비전 연산을 제공한다. 반면, ASIC은 설계 고정성을 전제로 하여 면적과 전력 효율을 극대화할 수 있다. 동일한 연산을 수행할 경우 ASIC은 FPGA 대비 30 %50 % 전력 절감과 2배 이상의 처리량 향상을 기대한다. 그러나 NRE(Non‑Recurring Engineering) 비용이 수백만 달러에 달하고, 설계 주기가 1218개월로 길어 빠르게 변하는 비전 알고리즘에 대응하기 어렵다. Structured ASIC은 ASIC과 FPGA 사이의 타협점으로, 표준 셀 기반 레이아웃에 부분적인 라우팅만을 커스터마이징함으로써 NRE 비용을 30 % 수준으로 낮추면서도 전력 효율을 15 %20 % 개선한다. 그러나 여전히 설계 주기가 69개월로 FPGA보다 길고, 라우팅 제약으로 인해 최고 클럭 주파수를 제한받는다.

논문은 또한 온보드 전원 관리와 열 설계 문제를 다룬다. 비전 연산이 집중되는 영역은 국부적인 열 집중을 일으키며, 소형 UAV의 냉각 메커니즘이 제한적이므로 전력 밀도 0.5 W/cm² 이하로 유지해야 한다. 이를 위해 동적 전압·주파수 스케일링(DVFS)과 전력 게이팅 기법을 적용한 FPGA 설계가 제시되며, 실험 결과 평균 전력 1.8 W, 피크 전력 2.3 W 수준을 달성했다.

결론적으로, 현재 소형 UAV의 시장 진입과 빠른 프로토타이핑 요구를 고려하면 FPGA가 가장 현실적인 선택이며, 대량 생산 단계에서 비용과 전력 효율을 최적화하고자 할 경우 Structured ASIC 혹은 ASIC으로 전환하는 단계적 로드맵이 제안된다.

📜 논문 원문 (영문)

🚀 1TB 저장소에서 고화질 레이아웃을 불러오는 중입니다...