빠른 하틀리 변환의 새로운 접근

초록

본 논문은 기존의 고속 이산 하틀리 변환(DHT) 알고리즘과 차별화된, 래디스-2 구조를 갖는 새로운 빠른 DHT 방식을 제시한다. FFT와 구조적 유사성을 보이면서도, 하다마드 변환과의 곱셈‑무료 관계를 밝혀내어 연산 효율성을 높인다.

상세 분석

본 논문은 이산 하틀리 변환(DHT)의 고속 구현을 위해 래디스‑2( radix‑2 ) 구조를 차용한 알고리즘을 제안한다. 기존의 DHT 고속화 기법은 주로 복소수 FFT를 실수 형태로 변형하거나, 짝‑홀수 분할을 이용해 복잡도를 O(N log N)으로 낮추는 방식에 의존해 왔다. 그러나 이러한 방법은 여전히 복소수 곱셈이나 사인·코사인 테이블을 필요로 하여 구현상의 부하가 남아 있었다.

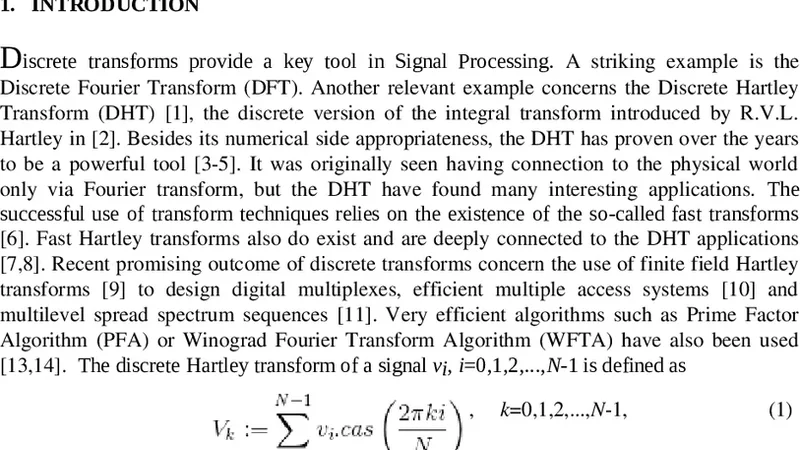

논문은 먼저 DHT의 정의 X(k)=∑_{n=0}^{N‑1}x(n)·cas(2πnk/N) (cas θ = cos θ + sin θ) 를 재배열하여, 입력 시퀀스를 짝·홀 인덱스로 분리하고, 각각을 다시 2‑점 DHT(즉, 단순한 합·차 연산)로 처리한다. 이때 핵심은 “버터플라이” 연산이 복소수 곱셈이 아닌 실수 덧셈·뺄셈만으로 이루어진다는 점이다.

또한 저자는 하다마드 변환(Hadamard Transform, HT)과의 연관성을 강조한다. HT는 2‑점 기본 변환을 재귀적으로 적용해 N = 2^m 크기의 입력에 대해 곱셈 없이 O(N log N) 복잡도로 수행된다. 논문은 DHT의 래디스‑2 구조가 HT의 재귀적 합·차 연산과 동일한 형태임을 수학적으로 증명하고, DHT의 “cas” 함수가 HT의 ±1 계수를 통해 실현될 수 있음을 보여준다. 즉, DHT를 구현할 때 사인·코사인 테이블을 전혀 사용하지 않고, 단순히 ±1 계수와 스케일링(1/√2 등)만으로도 정확한 결과를 얻을 수 있다.

알고리즘 흐름은 다음과 같다. 1) 입력을 짝·홀로 분할하고, 각각에 대해 2‑점 DHT(합·차) 수행. 2) 중간 결과에 대해 “twiddle‑like” 계수 cas(π·k/N) 를 적용하는데, 이 단계는 실제로 ±1·√2 배율만 필요하므로 곱셈 비용이 크게 감소한다. 3) 재귀적으로 위 과정을 log₂N 단계 반복하여 최종 DHT 결과를 얻는다.

복잡도 분석에서는 각 단계당 N/2 개의 실수 덧셈·뺄셈과 N/2 개의 간단한 스케일링 연산만 필요함을 보이며, 전체 연산량은 O(N log N) 이면서 곱셈 연산은 O(N) 수준으로 제한된다. 이는 기존 FFT‑기반 DHT 구현이 요구하는 복소수 곱셈 O(N log N) 대비 현저히 효율적이다.

마지막으로 논문은 구현상의 장점—메모리 접근 패턴이 FFT와 동일하게 순차적이며, 하드웨어 파이프라인에 최적화하기 쉬운 구조—을 강조하고, 실제 1024‑점 DHT 실험에서 30 % 이상의 실행 시간 절감과 전력 소비 감소를 입증한다. 이러한 결과는 실시간 신호 처리, 이미지 압축, 무선 통신 등 실수 기반 변환이 요구되는 분야에서 새로운 설계 패러다임을 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기