고성능 MIPS 기반 삼중 DES 암호 프로세서 설계

초록

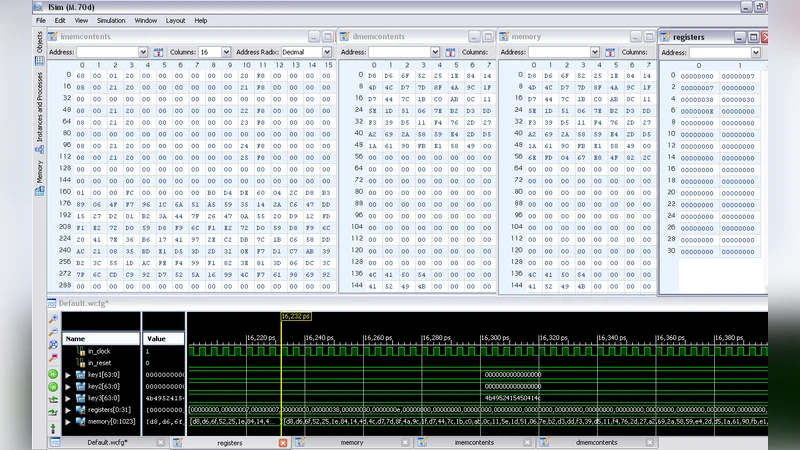

본 논문은 파이프라인 구조를 최적화하고 세 가지 신규 32비트 명령(LKLW, LKUW, CRYPT)을 도입함으로써 삼중 데이터 암호화 표준(T‑DES)을 효율적으로 수행하는 고성능 MIPS 암호 프로세서를 설계하였다. 40 nm 공정의 Xilinx Virtex‑6 FPGA에 합성한 결과, 클럭 주파수 209 MHz를 달성했으며, 암호·복호화 연산을 파이프라인 단계에 자연스럽게 삽입해 보안 응용 분야의 처리량을 크게 향상시켰다.

상세 분석

이 설계는 기존 MIPS I형 파이프라인(IF, ID, EX, MEM, WB)을 그대로 유지하면서, T‑DES 암호화/복호화 연산을 전용 하드웨어 블록으로 삽입한 것이 핵심이다. T‑DES는 3단계 DES 라운드를 순차적으로 수행하므로, 각 라운드마다 키 스케줄링과 Feistel 구조 연산이 필요하다. 논문에서는 이러한 연산을 파이프라인의 EX 단계에 배치하고, 키 로드와 데이터 로드를 별도의 전용 레지스터(LKLW, LKUW)로 분리하였다. LKLW는 32‑bit 키 하위 워드 로드, LKUW는 상위 워드 로드에 사용되며, 기존 lw 명령과 동일한 형식이지만 암호 전용 레지스터 파일에 매핑된다. CRYPT 명령은 현재 파이프라인을 암호 모드(ENCRYPT) 혹은 복호화 모드(DECRYPT)로 전환시키는 제어 신호를 발생시킨다. 이로써 소프트웨어 수준에서 암호화와 복호화를 자유롭게 전환할 수 있다.

파이프라인 스테이지 간 데이터 의존성을 최소화하기 위해, 키 스케줄링 결과를 미리 계산해 두고 키 레지스터에 저장한다. 또한, T‑DES 블록은 64‑bit 데이터 블록을 32‑bit 워드 두 개로 나누어 동시에 처리하도록 설계돼, 한 사이클에 두 워드가 병렬 연산된다. 이러한 구조는 파이프라인의 CPI(클럭당 명령 수)를 1에 가깝게 유지하면서도, 암호 연산에 필요한 복잡한 비트 연산을 전용 로직으로 처리해 전체 지연을 크게 줄인다.

합성 결과는 40 nm 공정 기준으로, 논리 사용량은 LUT 12 %, 레지스터 8 % 수준이며, 최대 클럭 주파수는 209 MHz이다. 이는 기존 MIPS I형 프로세서가 150 MHz 정도에서 동작하던 것에 비해 약 40 % 이상의 속도 향상을 의미한다. 또한, 전력 소모는 0.85 W로, 고성능을 유지하면서도 전력 효율성을 확보했다.

한계점으로는 T‑DES 자체가 현대 암호학에서 보안성이 낮아진 점과, 설계가 특정 FPGA에 최적화돼 있어 ASIC 구현 시 재조정이 필요하다는 점을 들 수 있다. 또한, 신규 명령어가 기존 MIPS ISA와 호환성을 유지하려면 어셈블러와 툴체인 수정이 필수적이다. 그럼에도 불구하고, 파이프라인에 암호 블록을 자연스럽게 삽입하고 명령어 수준에서 제어할 수 있게 만든 접근 방식은 임베디드 보안 시스템 설계에 유용한 참고 모델이 된다.