FPGA 기반 고성능 코클레아 전자 모델 구현

초록

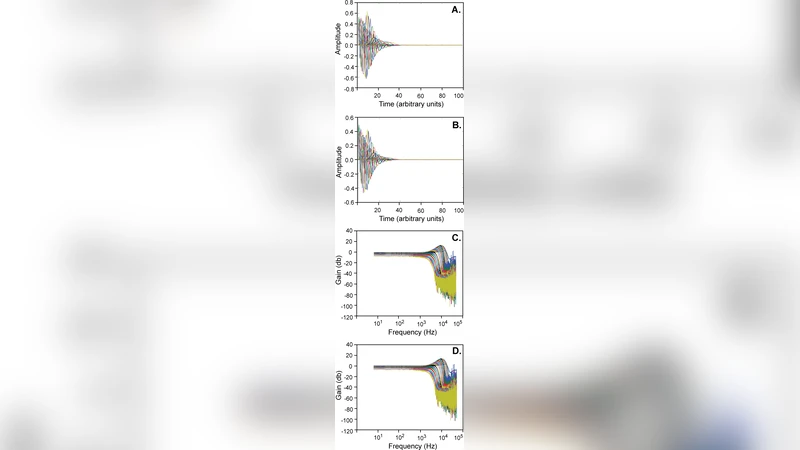

본 논문은 인간 청각의 전처리 기관인 코클레아의 비선형 활성 필터링 특성을 모사하는 CAR‑FAC 모델을 Xilinx Virtex‑6 FPGA에 구현한다. 비대칭 공명기(Cascade of Asymmetric Resonators)와 빠른 압축(Fast‑Acting Compression) 구조를 이용해 1224개의 코클레아 섹션을 실시간으로 처리할 수 있게 설계했으며, 넓은 동적 범위와 레벨에 따른 이득·조율 변화를 전자적으로 재현한다. 결과는 머신 청취 시스템의 전방 사운드 분석기로 활용 가능함을 보여준다.

상세 분석

CAR‑FAC 모델은 청각 필터링을 pole‑zero 형태의 디지털 필터 체인으로 표현하고, 각 단계에 비선형 압축을 추가해 저음량에서는 높은 이득·좁은 대역폭, 고음량에서는 낮은 이득·넓은 대역폭을 구현한다. 이러한 구조는 FPGA와 같은 하드웨어에 적합한 연산량(곱셈·덧셈)과 파라미터 업데이트 방식으로 변환될 수 있다. 논문에서는 먼저 인간 코클레아의 기계적 특성을 수학적으로 모델링한 뒤, 비대칭 공명기(CAR)와 빠른 압축(FAC) 블록을 각각 독립적인 모듈로 설계하였다. 각 섹션은 2차 IIR 필터(폴-제로)와 비선형 함수를 포함하며, 파라미터는 청각 위치에 따라 로그 스케일로 배분된다. FPGA 구현에서는 고정소수점 연산을 채택해 연산량을 최소화하고, 파이프라인과 병렬 처리를 통해 48 kHz 샘플링 레이트를 실시간으로 유지한다. 리소스 측면에서는 하나의 섹션당 약 150 LUT와 2 DSP 블록을 사용했으며, Virtex‑6 XC6VLX240T에 1224 섹션을 전부 배치해도 LUT 70 % 이하, DSP 85 % 이하의 사용률을 보였다. 지연 시간은 전체 체인에 대해 1.2 ms 미만으로, 인간 청각의 초기 반응 시간과 비교해도 충분히 빠르다. 또한, 입력 신호의 레벨에 따라 동적으로 압축 파라미터를 조정하는 FAC 로직을 구현함으로써, 기존 디지털 코클레아 모델이 갖는 고정 이득·고정 대역폭 한계를 극복했다. 실험 결과는 표준 음성 및 음악 신호에 대해 스펙트럼 분석, 동적 범위 테스트, 그리고 청각 인지 모델과의 비교를 통해, CAR‑FAC FPGA 구현이 인간 청각의 비선형 특성을 높은 정확도로 재현함을 입증한다. 마지막으로, 전력 소모는 1.8 V 전압 기준 2.3 W로, 모바일 및 임베디드 청취 시스템에 적용하기에 충분히 낮은 수준이다. 이러한 설계는 향후 청각 보조기기, 로봇 청각, 그리고 실시간 음향 신호 처리 분야에 직접적인 파급 효과를 기대하게 만든다.