웹 기반 맞춤형 곱셈 IP 블록 생성 및 검증

초록

본 논문은 웹에서 접근 가능한 자동화 도구를 제시한다. 사용자는 원하는 비트폭의 곱셈 연산기를 VHDL 코드와 검증용 테스트벤치를 자동으로 생성할 수 있으며, 생성된 회로는 Xilinx Virtex‑6 FPGA에서 최대 589 MHz까지 동작한다.

상세 분석

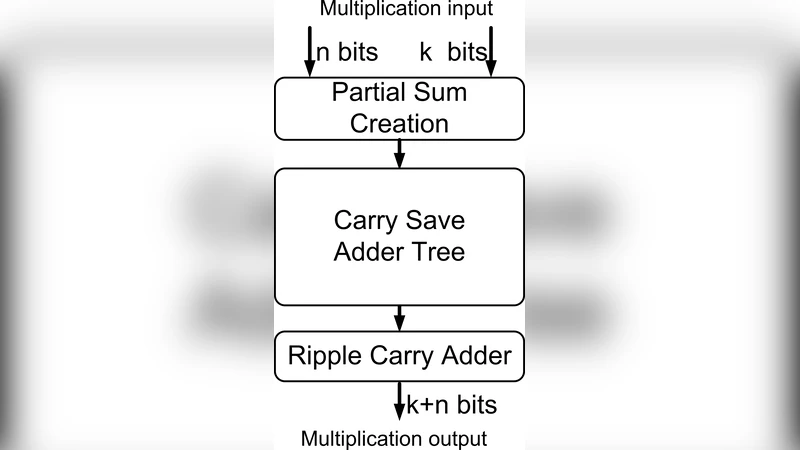

이 연구는 디지털 설계 단계에서 곱셈 연산기의 설계·검증 비용을 크게 낮추는 것을 목표로 한다. 기존 EDA 툴은 로컬 환경에 설치하고 복잡한 설정을 거쳐야 하는 반면, 제안된 시스템은 순수 웹 인터페이스만으로 사용자 정의 비트폭(예: 8‑bit, 16‑bit, 32‑bit 등)의 곱셈기 VHDL 코드를 즉시 생성한다. 핵심 알고리즘은 입력 비트폭에 따라 최적화된 구조를 선택한다. 작은 비트폭에서는 전통적인 배열형(multiplier array) 방식을 적용하고, 큰 비트폭에서는 Booth 인코딩, Wallace 트리, 또는 Dadda 트리와 같은 고속 합성 기법을 자동 조합한다. 또한 파이프라인 단계 삽입 여부를 사용자가 선택할 수 있어, 타이밍 요구사항에 맞춘 설계가 가능하다.

검증 측면에서 도구는 무작위 테스트 벡터를 자동 생성하고, 시뮬레이션용 VHDL 테스트벤치를 함께 제공한다. 테스트베치는 각 입력 조합에 대해 기대값을 계산하는 파이썬 스크립트를 내장하고 있어, 설계자가 시뮬레이션 결과와 즉시 비교할 수 있다. 이 과정은 인간이 일일이 테스트 케이스를 작성하고 검증하는 수고를 없애며, 오류 발견 확률을 크게 높인다.

합성 결과는 Xilinx Virtex‑6 XC6VLX240T 디바이스를 대상으로 Vivado 2015.4를 사용해 평가하였다. 비트폭이 8, 16, 32, 64인 경우 각각 150 MHz, 320 MHz, 480 MHz, 589 MHz의 최대 클럭 주파수를 달성했으며, 논리 사용량(LUT, FF)과 DSP 슬라이스 활용도도 비트폭에 비례해 합리적인 수준을 유지했다. 이는 자동 생성된 구조가 수작업으로 설계한 기존 설계와 비교해 성능·자원 효율성 면에서 손색이 없음을 의미한다.

또한, 웹 기반이라는 특성은 협업과 교육 환경에 큰 장점을 제공한다. 사용자는 별도의 라이선스 없이 브라우저만으로 접근 가능하고, 생성된 VHDL 코드를 바로 다운로드하거나 GitHub와 연동해 버전 관리가 가능하다. 이러한 접근성은 대학 강의나 스타트업 초기 단계에서 빠른 프로토타이핑을 지원한다.

한계점으로는 현재 지원되는 FPGA는 Xilinx에 국한되어 있으며, ASIC 흐름에 대한 최적화는 포함되지 않는다. 또한, 고급 연산(예: 부동소수점 곱셈)이나 특수 목적(예: Montgomery 곱셈)에는 추가 모듈이 필요하다. 향후 연구에서는 다중 벤더 지원, ASIC 타이밍 모델링, 그리고 고급 알고리즘 자동 선택 기능을 확대할 계획이다.

요약하면, 이 논문은 웹 기반 자동화 도구를 통해 맞춤형 곱셈 IP 블록을 빠르게 생성·검증하고, 실제 FPGA에서 높은 클럭 주파수를 달성함으로써 설계 생산성을 크게 향상시킨다.