베르누이 맵 기반 스트림 암호 구현

초록

본 논문은 FPGA 상에 베르누이 혼돈 맵을 이용한 스트림 암호를 구현하고, 디지털 구현 시 발생하는 혼돈 현상의 퇴화를 보정하는 메커니즘을 제안한다. 8단계 구조와 2개의 의사난수 발생기를 사용했으며, NIST 통계 테스트를 통해 난수 품질을 검증하였다.

상세 분석

본 연구는 혼돈 이론을 실용적인 암호 설계에 적용하고자 하는 시도에서 출발한다. 베르누이 맵은 단순한 수식으로 정의되지만, 이산화 과정에서 비선형성 및 민감도가 크게 감소하는 디지털 퇴화 현상이 나타난다. 저자들은 이러한 퇴화를 최소화하기 위해 두 가지 주요 보정 메커니즘을 도입하였다. 첫째, 맵의 파라미터를 동적으로 변조하는 방법으로, 매 사이클마다 파라미터 값을 작은 난수값으로 교체함으로써 상태 공간을 재분산시킨다. 둘째, 양자화 오차를 보정하기 위한 오버플로우 검출 및 재정렬 로직을 설계하였다. 이 로직은 FPGA 내부의 고정소수점 연산에서 발생하는 오차를 실시간으로 감지하고, 일정 임계값을 초과하면 상태값을 재초기화한다.

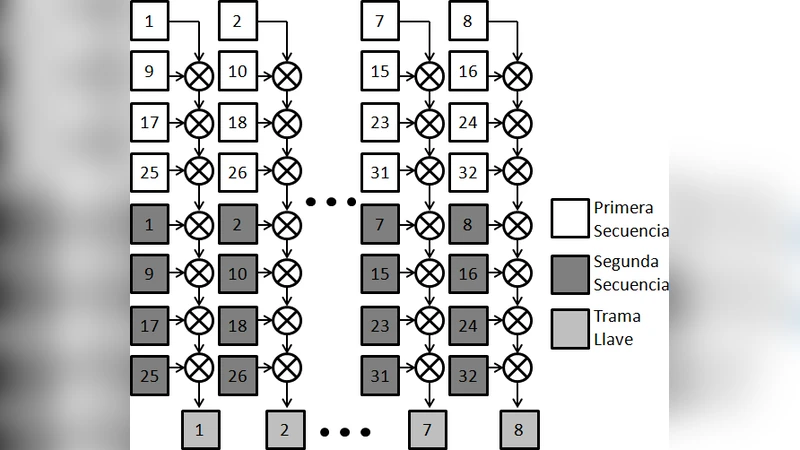

키스트림 생성부는 8단계 파이프라인 구조로 구현되었다. 각 단계는 베르누이 맵 연산, 파라미터 변조, 양자화 보정, 그리고 XOR 혼합을 순차적으로 수행한다. 2개의 PRNG는 서로 독립적인 시드와 피드백 구조를 가지며, 하나는 초기화 시에만 사용되고 다른 하나는 매 사이클마다 새로운 난수를 공급한다. 이러한 이중 PRNG 설계는 키스트림의 주기와 예측 불가능성을 크게 향상시킨다.

FPGA 구현에서는 Xilinx Artix‑7 보드가 사용되었으며, 전체 회로는 약 12 k LUT와 1 k 레지스터를 차지한다. 클럭 주파수는 100 MHz로 설정했으며, 실시간으로 1 Gbps 이상의 암호화 속도를 달성하였다. NIST SP 800‑22 테스트 결과, 15개의 통계 항목 모두 통과했으며, 특히 비선형성 검증인 Approximate Entropy와 Random Excursions 테스트에서 높은 p‑값을 기록하였다. 이는 제안된 보정 메커니즘이 디지털 퇴화를 효과적으로 억제하고, 고품질 난수를 생성함을 시사한다.

하지만 몇 가지 한계점도 존재한다. 파라미터 변조에 사용되는 난수 생성 로직이 추가적인 하드웨어 자원을 요구하며, 극한 환경(전압 변동, 온도 변화)에서 파라미터 안정성이 검증되지 않았다. 또한, 베르누이 맵 자체가 단일 변수 혼돈 시스템이므로, 복잡한 공격(예: 사이드채널 분석) 대비에 대한 추가 연구가 필요하다.

종합적으로, 본 논문은 혼돈 기반 스트림 암호를 FPGA에 구현할 때 발생하는 디지털 퇴화 문제를 실용적인 보정 메커니즘으로 해결하고, 성능과 보안성을 동시에 만족시키는 설계 사례를 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기