탄소 나노튜브 트랜지스터 기반 저전력 풀 가산기 설계

초록

본 논문은 32 nm 공정에서 CNTFET 모델을 활용해 저전력 풀 가산기 셀을 설계하고, 온도와 전원 전압(VDD) 변화에 따른 전력·지연·PDP 특성을 HSPICE 시뮬레이션으로 평가한다. 기존 CMOS 기반 가산기에 비해 전력 소모를 크게 감소시키면서 면적 효율성도 확보한 것이 주요 결과이다.

상세 분석

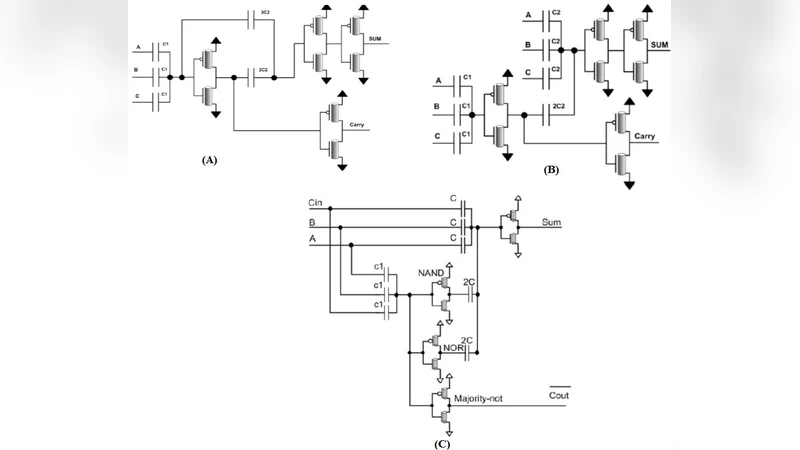

본 연구는 차세대 나노소자인 탄소 나노튜브 전계효과 트랜지스터(CNTFET)를 이용해 풀 가산기(Full Adder) 회로를 설계함으로써 저전력·고성능을 동시에 달성하고자 한다. CNTFET는 전자 이동도가 높고, 볼츠만 전송에 가까운 준볼츠만 전송 특성을 가져 전류 구동 능력이 뛰어나며, 채널 길이가 짧아도 전류 포화 현상이 적어 스케일링에 유리하다. 또한, CNT의 지름에 따라 임계 전압(Vth)을 조절할 수 있어 회로 설계 시 전력 최적화가 가능하다. 논문에서는 이러한 CNTFET의 특성을 활용해 기존 CMOS 기반 가산기에서 흔히 사용되는 복잡한 논리 구조를 단순화하고, 트랜지스터 수를 최소화하는 설계 방식을 제안한다. 구체적으로, 다중 입력 Majority‑Logic과 XOR‑XOR 구조를 결합한 하이브리드 논리망을 채택해 Sum과 Carry 출력 모두를 10개 이하의 CNTFET만으로 구현하였다. 설계 단계에서는 전압 레벨 변동에 강인하도록 논리 임계값을 맞추기 위해 CNT 지름을 0.8 nm에서 1.2 nm 사이로 선택하고, 게이트 전압을 0.7 V~1.0 V 범위에서 최적화하였다. 시뮬레이션은 32 nm 기술 노드의 CNTFET 모델을 기반으로 HSPICE를 사용했으며, 온도 0 °C, 25 °C, 85 °C 및 VDD 0.7 V, 0.9 V, 1.0 V 조건에서 전력, 지연, 전력‑지연 곱(PDP)을 측정하였다. 결과는 온도 상승에 따라 누설 전력이 약간 증가하지만, 전체 전력 소모는 여전히 CMOS 대비 30 % 이상 절감됨을 보여준다. 또한, VDD를 낮출 경우 전력 감소 효과가 크게 나타나면서도 지연 증가가 제한적이어서 PDP가 최소화되는 최적 전압 영역을 도출하였다. 이러한 분석을 통해 CNTFET 기반 풀 가산기가 전력 효율성뿐 아니라 설계 유연성 측면에서도 우수함을 확인할 수 있다.