스캔 체인 설계 공동 에뮬레이션을 위한 SCEMI 기반 고속 검증 방법

초록

본 논문은 대규모 SoC의 스캔 체인 검증에 소요되는 시간을 크게 단축하기 위해 SCE‑MI 프로토콜과 FPGA 기반 에뮬레이션 플랫폼을 결합한 방법론을 제시한다. SystemC 테스트벤치와 FPGA 합성 가능한 트랜잭터를 이용해 ISCAS89 S400 벤치마크 회로를 구현하고, 기존 RTL 시뮬레이션, 시뮬레이션 가속, 트랜잭션 기반 에뮬레이션과 비교했을 때 82 % 빠른 성능을 보이며 MHz 수준의 실행 속도를 달성한다.

상세 분석

이 연구는 스캔 체인 검증이 레지스터 수에 비례해 복잡도가 급격히 증가한다는 전제에서 출발한다. 전통적인 RTL 시뮬레이션은 클럭당 몇 사이클 정도밖에 진행되지 못해 수백만 개 이상의 플립플롭을 포함하는 대형 SoC에서는 실용적이지 않다. 논문은 이러한 문제를 해결하기 위해 SCE‑MI(Software‑Controlled Emulation‑Machine Interface)라는 고속 호스트‑에뮬레이터 통신 프로토콜을 활용한다. SCE‑MI는 메모리 매핑 기반의 명령/데이터 전송 방식을 제공해 호스트 CPU와 FPGA 에뮬레이터 간에 마이크로초 단위의 레이턴시로 대용량 트랜잭션을 주고받을 수 있다.

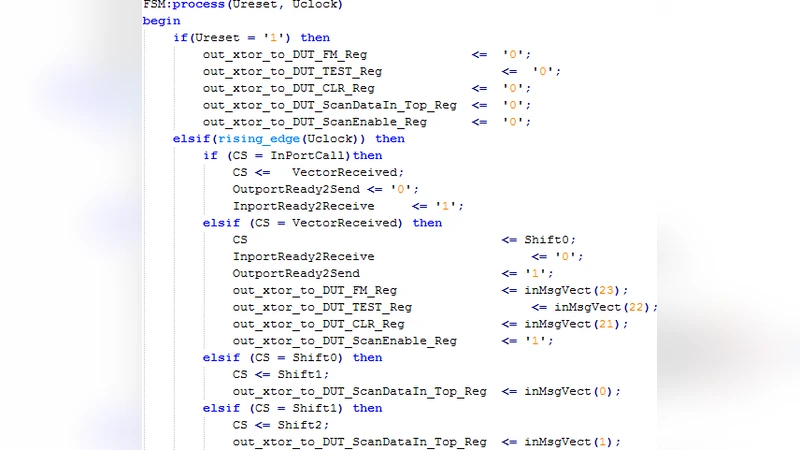

구현 측면에서 저자들은 두 단계의 트랜잭터 모델을 설계한다. 첫 번째는 SystemC 수준에서 스캔 시퀀스를 생성하고, 이를 SCE‑MI 패킷으로 변환하는 소프트웨어 트랜잭터이다. 두 번째는 FPGA 내부에 배치되는 하드웨어 트랜잭터로, 수신된 패킷을 디코딩해 스캔 체인 레지스터에 직접 쓰거나 읽는 역할을 한다. 이 구조는 기존의 파이프라인 기반 시뮬레이션 가속기와 달리, 스캔 데이터가 메모리 매핑된 레지스터 파일에 직접 매핑되므로 클럭당 하나의 사이클만으로 전체 스캔 체인을 순회할 수 있다.

성능 평가에서는 ISCAS89 S400 벤치마크(다중 레지스터와 복잡한 피드백 루프를 포함)를 대상으로 네 가지 방법을 비교한다. 순수 RTL 시뮬레이션은 1 GHz 클럭에서도 실제 시뮬레이션 속도는 Hz 수준에 머물렀다. 시뮬레이션 가속은 하드웨어 가속기를 이용해 kHz 수준까지 끌어올렸지만, 트랜잭션 오버헤드와 동기화 비용이 여전히 병목이었다. 트랜잭션 기반 에뮬레이션은 SCE‑MI 없이 자체 프로토콜을 사용했으며, 서브 메가헤르츠 수준에 머물렀다. 반면 제안된 SCE‑MI 기반 공동 에뮬레이션은 평균 3.6 MHz의 실행 속도를 기록했으며, 이는 기존 방법 대비 82 % 이상의 속도 향상을 의미한다.

또한, MHz 수준의 실행 속도는 소프트웨어 스택(드라이버, 운영체제, 애플리케이션)과의 통합을 가능하게 한다. 이는 DFT(Design‑for‑Test) 전략을 실제 운영 환경에 가깝게 검증할 수 있음을 의미한다. 논문은 이러한 통합이 타이밍 검증, 전력 분석, 그리고 실시간 오류 복구 메커니즘 개발에 직접적인 이점을 제공한다는 점을 강조한다. 마지막으로, 제안된 방법은 FPGA 리소스 사용량이 비교적 낮아 기존 프로토타이핑 흐름에 쉽게 삽입될 수 있으며, 설계자들이 스캔 체인 외에도 메모리 인터페이스, 버스 프로토콜 등 복합적인 DFT 시나리오를 동시에 검증할 수 있는 확장성을 제공한다.