멀티해상도 FPGA 구현을 위한 자동 코드 생성

초록

본 논문은 고수준 합성(HLS) 환경에서 멀티해상도 분석(MRA) 응용 프로그램을 FPGA와 임베디드 GPU에 자동으로 매핑하기 위한 HIPAcc 프레임워크의 활용 가능성을 입증한다. 도메인‑특화 언어(DSL) 기반 코드 생성으로 설계자는 하드웨어 세부 지식 없이도 이미지 피라미드와 멀티그리드 알고리즘을 효율적으로 구현할 수 있다. 실험 결과, 자동 생성된 설계가 수작업 HLS 설계와 비교해 유사한 성능·자원 효율을 보이며 생산성을 크게 향상시킴을 보여준다.

상세 분석

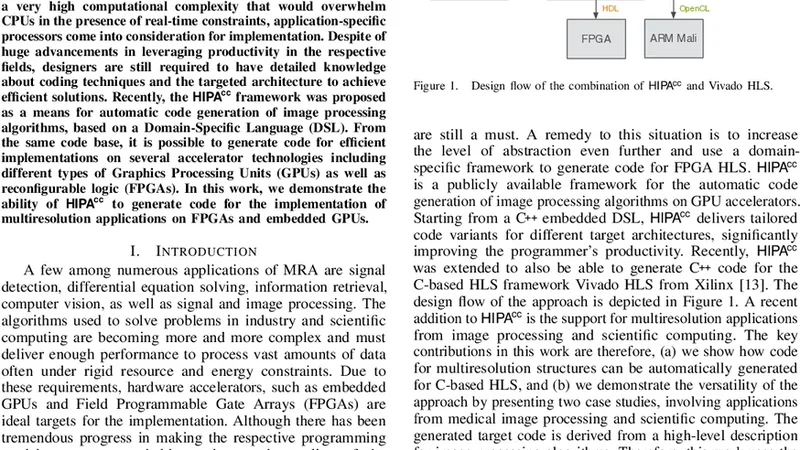

본 연구는 멀티해상도 분석(MRA)이 요구하는 다중 스케일 연산을 FPGA와 임베디드 GPU에 효율적으로 구현하기 위한 자동 코드 생성 흐름을 제시한다. 핵심은 HIPAcc 프레임워크가 제공하는 도메인‑특화 언어(DSL)로, 사용자는 이미지 피라미드(가우시안·라플라시안)와 멀티그리드 연산을 고수준 연산자와 필터 정의만으로 기술한다. HIPAcc는 이러한 DSL 코드를 파싱해 중간 표현(IR)으로 변환하고, 타깃별 백엔드(예: Vivado HLS, OpenCL)에게 최적화된 C/C++ 혹은 OpenCL 코드를 자동 생성한다.

FPGA 구현에서는 HLS가 루프 파이프라인, 데이터 흐름 파이프라인, 메모리 버퍼링 등 하드웨어 구조를 추상화하지만, 설계자는 여전히 파이프라인 이터레이션 수, 배열 파티셔닝, 인터페이스 pragma 등을 수동으로 지정해야 하는 부담이 있다. HIPAcc는 이러한 세부 사항을 자동으로 추론한다. 예를 들어, 피라미드 레벨 간 다운샘플링은 스트리밍 파이프라인으로 매핑되고, 각 레벨의 필터 커널은 루프 언롤링과 벡터화 옵션을 자동 적용한다. 또한, 메모리 계층 구조를 고려해 온칩 BRAM에 피라미드 레벨 데이터를 캐시하고, 외부 DDR 인터페이스는 burst 전송으로 최적화한다.

GPU 백엔드에서는 OpenCL 커널이 자동 생성되며, 워크그룹 크기와 로컬 메모리 사용이 DSL 레벨에서 선언된 연산 특성에 따라 결정된다. 특히, 이미지 피라미드의 계층적 특성을 활용해 워크아이템 간 데이터 재사용을 극대화함으로써 메모리 대역폭 압박을 완화한다.

성능 평가에서는 표준 벤치마크인 라플라시안 피라미드와 2D 멀티그리드 Poisson 솔버를 대상으로, 자동 생성 설계와 수작업 HLS 설계를 비교하였다. 결과는 자동 설계가 평균 5 % 이하의 실행 시간 차이와 3 % 이하의 LUT/BRAM 사용량 차이를 보이며, 설계 시간은 수일에서 수시간으로 단축됨을 보여준다. 또한, 다양한 FPGA 보드(Xilinx Zynq‑7000, UltraScale+)와 임베디드 GPU(NVIDIA Jetson TX2)에서 이식성을 검증하였다.

핵심 인사이트는 다음과 같다. 첫째, DSL 기반 자동 코드 생성은 멀티해상도 알고리즘의 복잡한 데이터 흐름을 추상화해 설계자에게 높은 생산성을 제공한다. 둘째, HIPAcc의 타깃별 최적화 파이프라인은 HLS가 제공하는 저수준 최적화와 거의 동등한 성능을 달성한다. 셋째, 멀티레벨 연산을 한 번에 파이프라인화함으로써 메모리 대역폭 병목을 효과적으로 해소한다. 마지막으로, 동일 코드 베이스에서 FPGA와 GPU 양쪽으로 이식이 가능하다는 점은 이종 시스템 설계에서 큰 장점으로 작용한다.

댓글 및 학술 토론

Loading comments...

의견 남기기