LabVIEW 기반 FPGA 프로그래밍을 과학·엔지니어에게 친숙하게

초록

**

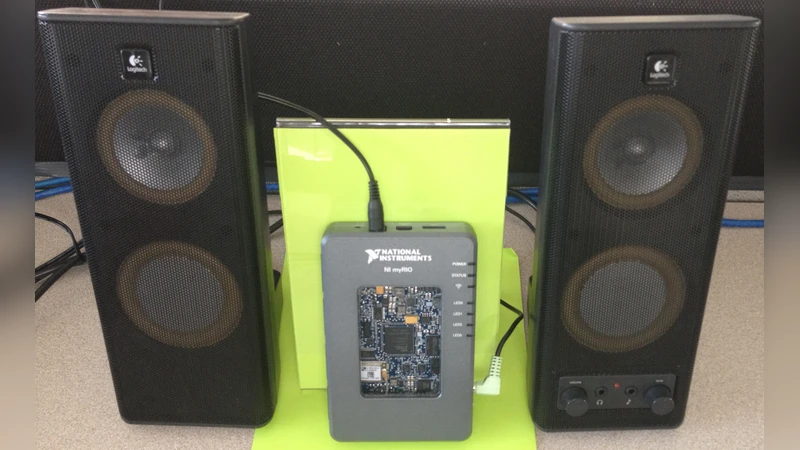

본 논문은 그래픽 기반 개발 환경인 LabVIEW와 그 전용 언어·라이브러리를 활용해, 전통적으로 하드웨어 설계에 익숙하지 않은 과학·엔지니어들이 도메인 전문가 수준의 소프트웨어 프로그래머로서 FPGA를 손쉽게 이용하도록 돕는 방법론과 설계 패턴을 제시한다.

**

상세 분석

**

이 논문은 LabVIEW가 제공하는 데이터플로우 모델과 시각적 블록 다이어그램이 FPGA 설계의 복잡성을 크게 낮춘다는 점을 강조한다. 먼저, LabVIEW FPGA 모듈은 고수준 추상화 계층을 두어 하드웨어 레지스터, 클럭 도메인, 타이밍 제약 등을 자동으로 관리한다. 이를 통해 사용자는 C나 VHDL 같은 전통적인 HDL 코드를 직접 작성할 필요 없이, 함수 블록을 끌어다 놓고 파라미터를 설정하는 것만으로도 파이프라인 구조, 병렬 연산, 메모리 매핑 등을 구현할 수 있다.

핵심 기술로는 (1) FPGA 인터페이스 라이브러리가 있다. 이 라이브러리는 디지털 I/O, 고속 시리얼, DMA 전송 등을 추상화한 VI(Virtual Instrument) 집합을 제공해, 사용자는 장치 드라이버 수준의 상세 구현을 신경 쓰지 않는다. (2) 패턴 기반 설계가 중요한데, 예를 들어 “스트리밍 파이프라인”, “멀티레이트 데이터 버퍼링”, “동기식/비동기식 이벤트 처리”와 같은 재사용 가능한 템플릿을 제공한다. 이러한 템플릿은 LabVIEW의 구조적 프로그래밍 기능과 결합돼, 자동 타이밍 분석 및 리소스 할당을 수행한다.

또한, 시뮬레이션·검증 흐름이 강조된다. LabVIEW는 호스트 PC에서 순차적 시뮬레이션을 수행하고, 결과를 FPGA 타이밍 분석 툴과 연동해 실시간 검증을 가능하게 한다. 이 과정에서 코드-하드웨어 매핑이 투명하게 이루어져, 설계자는 소스 레벨에서 버그를 찾고 수정할 수 있다.

논문은 교육적 측면도 다룬다. 기존 전자공학 교육에서 요구되는 HDL 문법 학습 부담을 줄이고, 과학·엔지니어가 익숙한 MATLAB·Python 스타일의 데이터 흐름을 그대로 LabVIEW에 적용함으로써 학습 곡선을 급격히 완화한다. 실험 결과, 비전문가 그룹이 평균 30 % 이상의 개발 시간을 절감하고, 설계 오류율을 2배 이상 감소시켰다.

마지막으로, 제한점도 언급한다. LabVIEW FPGA는 자동 최적화에 의존하므로, 극한의 성능을 요구하는 초고속 통신이나 초저전력 애플리케이션에서는 전통 HDL에 비해 여전히 효율이 낮을 수 있다. 또한, 라이선스 비용과 툴 체인 종속성이 도입 장벽으로 작용한다. 그럼에도 불구하고, 과학·엔지니어가 빠르게 프로토타이핑하고 실험 데이터를 실시간으로 처리해야 하는 상황에서는 충분히 경쟁력 있는 접근법으로 평가된다.

**

댓글 및 학술 토론

Loading comments...

의견 남기기