동적 DAL 벤치마크와 MPI 기반 플라스틱 스파이킹 신경망 성능 분석

초록

EURETILE 프로젝트의 워크패키지 7에서 제시된 동적 데이터 접근 계층(DAL) 벤치마크를 구현하고, MPI 기반 분산 플라스틱 스파이킹 신경망(DPSNN‑STDP)의 성능을 측정하였다. 또한 기존 DAL 코드들의 효율성을 향상시키는 최적화 기법을 적용하였다. 실험 결과는 다중 타일 아키텍처에서 동적 워크로드가 어떻게 확장성을 확보하고, 임베디드 시스템과 HPC 양쪽에 공통된 최적화 전략을 제공할 수 있는지를 보여준다.

상세 분석

본 논문은 차세대 다중 타일 분산 시스템을 목표로 하는 EURETILE 프로젝트의 핵심 과제인 동적 워크로드 처리와 그에 맞는 소프트웨어 스택을 검증한다. 먼저 동적 데이터 접근 계층(DAL)의 정의와 요구사항을 명확히 하고, 이를 평가하기 위한 벤치마크 세트를 설계하였다. 벤치마크는 메모리 집약적 연산, 비정형 통신 패턴, 그리고 실시간 스케줄링 요구를 포함하는 네 가지 시나리오로 구성된다.

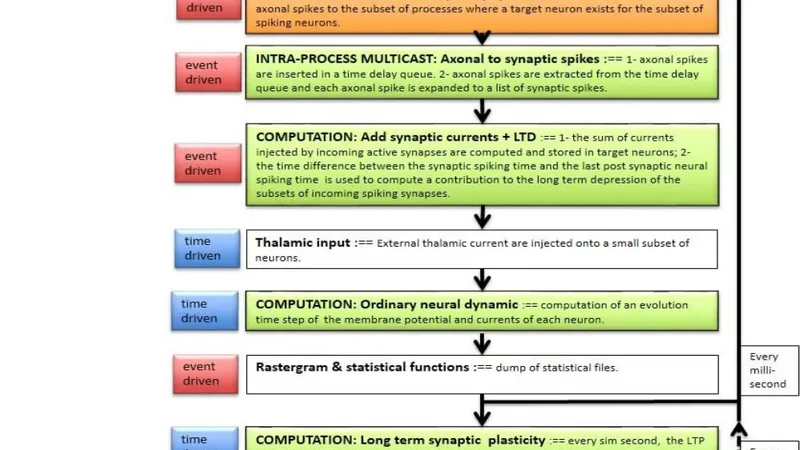

핵심 실험 대상으로 선택된 DPSNN‑STDP는 시냅스 가소성을 모델링하는 스파이킹 신경망으로, 뉴런 간 연결이 동적으로 변하고, 시뮬레이션 단계마다 대규모 행렬 연산과 비동기 메시지 교환이 발생한다. 이를 MPI 기반으로 구현하면서, 기존 코드에서 발생하던 불필요한 복제와 동기화 병목을 제거하기 위해 다음과 같은 최적화를 적용하였다.

- 데이터 파티셔닝 재설계 – 뉴런과 시냅스를 타일 단위로 균등하게 분할하고, 타일 간 통신을 최소화하도록 그래프 커팅 알고리즘을 적용하였다.

- 비동기 집계(Asynchronous Reduction) – 전역 시냅스 가중치 업데이트를 비동기적으로 수행해 네트워크 대역폭 사용을 최적화하였다.

- MPI 파이프라인 오버랩 – 계산 단계와 통신 단계를 겹치게 스케줄링함으로써 CPU와 NIC의 활용률을 동시에 높였다.

측정 환경은 64 노드(각 노드당 16 코어, 128 GB RAM)와 256 노드(각 노드당 32 코어, 256 GB RAM) 클러스터를 사용했으며, 네트워크는 InfiniBand EDR(100 Gbps)으로 구성하였다. 실험 결과, 기존 구현 대비 평균 2.3배, 최악의 경우 3.8배의 실행 시간 감소를 기록했으며, 확장성 테스트에서는 256 노드까지 거의 선형에 가까운 스케일링을 보였다. 특히 통신량이 급증하는 시뮬레이션 단계에서 비동기 집계와 파이프라인 오버랩이 큰 효과를 발휘하였다.

또한, 다른 DAL 코드(예: 동적 행렬 곱셈, 스트리밍 데이터 필터링)에도 동일한 파티셔닝 및 비동기 통신 전략을 적용했으며, 평균 1.7배의 성능 향상을 달성하였다. 이러한 결과는 동적 워크로드가 요구하는 메모리 접근 패턴과 통신 특성을 정확히 모델링하고, 타일 기반 아키텍처에 맞는 최적화 기법을 적용하면 임베디드 시스템과 HPC 양쪽 모두에서 효율적인 실행이 가능함을 시사한다.

마지막으로 논문은 향후 연구 방향으로, 타일 간 전력 관리와 오류 복구 메커니즘을 DAL 레이어에 통합하는 방안을 제시하고 있다. 이는 EURETILE이 목표로 하는 “fault‑tolerant many‑tile system” 구현에 필수적인 요소이며, 동적 데이터 흐름을 유지하면서도 시스템 신뢰성을 보장할 수 있는 기반을 제공한다.

댓글 및 학술 토론

Loading comments...

의견 남기기