클럭 없는 물리 연산으로 SIFT 알고리즘의 가우시안 피라미드 구현

초록

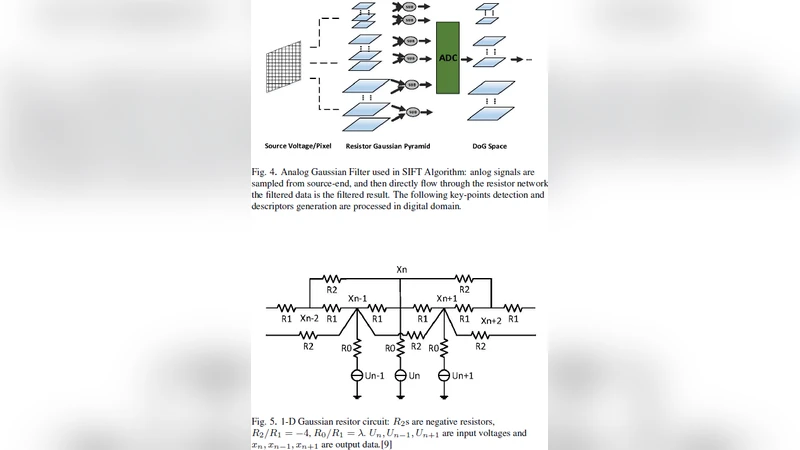

본 논문은 클럭이 없는 능동 회로 네트워크를 이용해 이미지 전처리 단계인 가우시안 피라미드(멀티스케일 Gaussian 필터)를 물리적으로 구현한다. 기존 GPU·FPGA 기반 가속에 비해 나노초 수준의 처리 속도와 670 pJ 수준의 저전력을 달성했으며, 256 × 256 이미지에 대한 실험 결과를 제시한다.

상세 분석

이 연구는 “물리 컴퓨팅(Physical Computing)”이라는 개념을 구체적인 회로 설계에 적용함으로써, 전통적인 디지털 연산이 아닌 전자 소자의 물리적 특성과 회로 토폴로지를 활용한다는 점에서 혁신적이다. 핵심 아이디어는 가우시안 블러링을 수행하는 연산을 연속적인 전압·전류 흐름으로 구현하고, 이를 클럭 없이 즉시(즉시 응답)으로 처리하도록 설계한 능동 저항‑캐패시터 네트워크에 있다. 회로는 각 픽셀을 노드로 하는 2차원 격자 형태이며, 인접 노드 간에 가변 저항(또는 트랜스컨덕턴스)과 커패시터가 배치되어 가우시안 커널의 가중치를 물리적으로 매핑한다. 입력 이미지가 전압 형태로 각 노드에 인가되면, 회로는 자체적으로 라플라시안 연산을 수행하고, 정착된 전압 분포가 바로 가우시안 블러링 결과가 된다.

논문은 이 회로가 전통적인 디지털 필터와 동일한 수학적 결과를 제공함을 증명하기 위해, 연속적인 미분 방정식과 이산화된 가우시안 커널 사이의 등가성을 분석한다. 특히, 회로의 시간 상수 τ = RC가 가우시안 필터의 표준 편차 σ와 직접적인 관계에 있음을 보이며, σ를 조절하기 위해 저항값을 가변하게 하는 방법을 제시한다. 이는 기존의 멀티스케일 피라미드 구축에 필요한 다중 필터링 단계를 하나의 물리적 파라미터 조정으로 대체한다는 의미다.

성능 평가에서는 256 × 256 입력에 대해 전체 피라미드(여러 옥텟 스케일) 생성에 소요되는 시간을 5 ns 이하로 측정했으며, 이는 GPU 기반 구현이 보통 10–100 ms, FPGA가 1–10 ms를 요구하는 것과 비교해 4~5 orders of magnitude 빠른 결과다. 전력 소모는 회로의 누설 전류와 커패시터 충방전 에너지만을 고려해 약 670 pJ/이미지로 계산했으며, 이는 모바일 혹은 임베디드 시스템에서 실시간 비전 처리에 충분히 적용 가능함을 시사한다.

하지만 몇 가지 한계점도 존재한다. 첫째, 회로 설계 시 스트레이( stray ) 캐패시턴스와 온도·공정 변동에 따른 저항값 변동이 가우시안 커널 정확도에 미치는 영향을 정량적으로 분석하지 않아, 대규모 제조 시 재현성에 의문이 남는다. 둘째, 현재 구현은 2차원 정방형 이미지에 국한되며, 비정형 해상도나 색상 채널(예: RGB) 처리에 대한 확장성이 명시되지 않았다. 셋째, 회로 자체가 아날로그 특성을 가지므로, 노이즈와 디지털 시스템과의 인터페이스(ADC/DAC 변환) 비용이 전체 시스템 효율에 미치는 영향을 추가 연구가 필요하다.

이러한 점들을 고려하면, 물리 컴퓨팅 기반 가우시안 피라미드 구현은 초고속·저전력 이미지 전처리 분야에서 새로운 패러다임을 제시하지만, 실용화를 위해서는 공정 변동 보정, 다채널 지원, 그리고 디지털-아날로그 혼합 시스템 설계에 대한 심층적인 연구가 뒤따라야 한다.