쿼리 DAG로 구현하는 실용적인 베이지안 네트워크 추론

초록

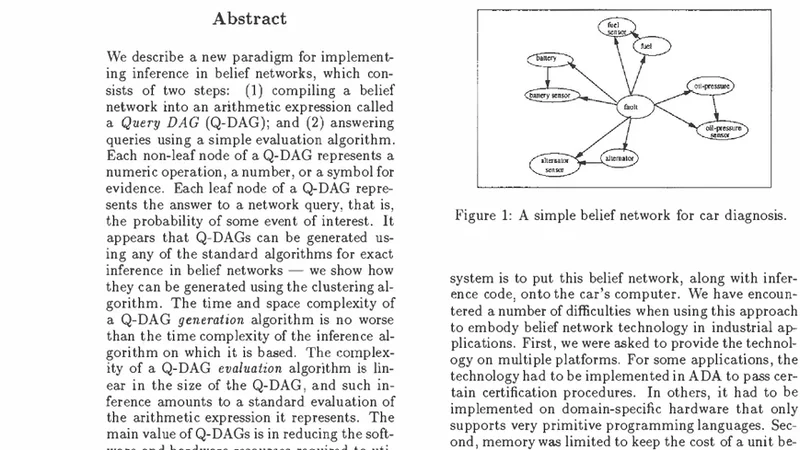

본 논문은 베이지안 네트워크의 추론을 위해 네트워크를 산술식 형태인 Query DAG(Q‑DAG)로 컴파일하는 새로운 패러다임을 제시한다. Q‑DAG의 내부 노드는 연산, 상수, 증거 기호를, 잎 노드는 질의 결과 확률을 나타낸다. 클러스터링·컨디셔닝 등 기존 정확 추론 알고리즘을 기반으로 Q‑DAG를 생성할 수 있으며, 생성 복잡도는 원 알고리즘과 동등하고, 평가 복잡도는 Q‑DAG 크기에 선형이다. 이 구조는 소프트웨어·하드웨어 구현 비용을 크게 낮추고, 다양한 플랫폼에서 실시간 추론을 가능하게 한다.

상세 분석

Q‑DAG(Query Directed Acyclic Graph) 개념은 베이지안 네트워크의 전통적인 추론 과정을 산술 표현식으로 변환한다는 점에서 혁신적이다. 기존 방법은 증거가 주어질 때마다 복잡한 메시지 전달이나 변수 소거를 수행해야 하지만, Q‑DAG는 사전에 모든 가능한 연산 흐름을 그래프 형태로 고정한다. 비잎 노드는 덧셈·곱셈 같은 기본 연산을, 증거 기호 노드는 관측값에 따라 선택적으로 활성화되는 파라미터를 나타낸다. 잎 노드는 최종 질의, 즉 특정 변수 조합의 사후 확률을 반환한다.

논문은 두 가지 전통적인 정확 추론 알고리즘—클러스터링(조인 트리)과 조건부(조건화) 방법—을 Q‑DAG 생성에 적용하는 절차를 상세히 제시한다. 클러스터링 기반에서는 조인 트리의 각 클러스터에 대해 지역 확률 테이블을 산술식으로 전개하고, 트리 구조를 따라 연산 노드를 연결한다. 조건화 기반에서는 증거 변수에 대한 경우 분할을 수행하고, 각 경우에 대한 부분 그래프를 만든 뒤, 최종적으로 공통 부분을 공유함으로써 그래프 크기를 최소화한다.

시간·공간 복잡도 분석에 따르면, Q‑DAG 생성 단계는 원 알고리즘의 실행 시간과 동일하거나 그 이하이며, 메모리 사용량도 동일한 차수이다. 평가 단계는 단순히 그래프를 한 번 순회하면서 연산을 수행하므로, 복잡도는 O(|Q‑DAG|)이다. 이는 실시간 시스템에서 증거가 변할 때마다 전체 네트워크를 재계산해야 하는 전통적 방식에 비해 획기적인 성능 향상을 제공한다.

또한, Q‑DAG는 하드웨어 구현에 유리한 특성을 가진다. 연산 노드가 고정된 형태이므로 FPGA나 ASIC에 직접 매핑하기 쉽고, 증거 기호 노드만 동적으로 제어하면 된다. 소프트웨어 측면에서도 평가 루틴이 매우 간단해, 제한된 메모리·CPU 환경에서도 안정적인 추론이 가능하다.

연구 방향으로는 Q‑DAG의 크기 최적화(공통 서브그래프 공유, 압축 기법), 근사 추론과의 결합(예: 샘플링 기반 부분 그래프 생성), 그리고 동적 네트워크 구조 변화에 대한 적응 메커니즘이 제시된다. 이러한 확장은 Q‑DAG가 실시간 의료 진단, 로봇 제어, 임베디드 시스템 등 다양한 응용 분야에 적용될 수 있는 기반을 마련한다.