이미지 신호 처리 설계 검증 환경의 조기 개발: TLM 기반 RTL 레퍼런스 모델 활용

초록

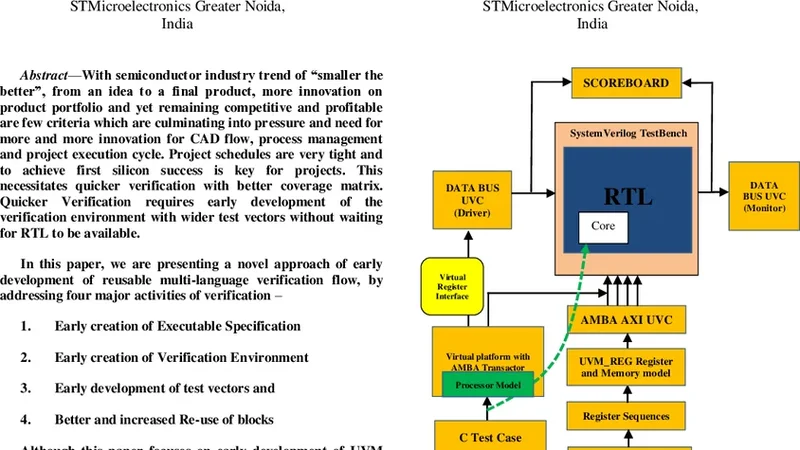

본 논문은 이미지 신호 처리(IP) 설계의 RTL이 완성되기 전에 시스템레벨 TLM 모델을 이용해 UVM 검증 환경을 사전 구축하는 방법을 제시한다. 실행 가능한 사양 작성, 검증 환경 초기화, 테스트 벡터 자동 생성, 블록 재사용성을 강화함으로써 검증 주기를 단축하고 커버리지를 향상시킨다.

상세 분석

본 연구는 반도체 설계 흐름에서 “작을수록 좋다”는 트렌드와 급격히 압축되는 프로젝트 일정에 대응하기 위해, RTL이 아직 미완성인 단계에서 검증 인프라를 조기에 마련하는 전략을 제안한다. 핵심은 이미지 신호 처리(IP) 설계에 특화된 TLM(Transaction Level Modeling) 레퍼런스 모델을 SystemC로 구현하고, 이를 UVM 기반 검증 환경에 연결하는 것이다. 먼저, 실행 가능한 사양(Executable Specification)을 SystemC TLM 모델로 정의함으로써 기능적 기대치를 명확히 하고, 이 모델을 ‘골드 모델’로 활용한다. 이후, UVM 테스트벤치는 SystemVerilog와 SystemC 사이의 DPI(Direct Programming Interface) 혹은 UVM‑ML(Multi‑Language) 플러그인을 통해 TLM 모델과 통신한다. 이렇게 하면 테스트벤치가 RTL이 아닌 레퍼런스 모델을 대상으로 시뮬레이션을 수행할 수 있어, RTL이 제공되기 전에도 광범위한 테스트 시나리오를 실행하고 커버리지를 측정할 수 있다.

또한, 논문은 검증 환경을 모듈화된 UVC(Universal Verification Component) 형태로 설계하여 재사용성을 극대화한다. 이미지 파이프라인의 각 단계(예: 색상 변환, 필터링, 디지털 변환)를 독립적인 UVC로 구현하고, 이들을 매개변수화된 시퀀스와 함께 조합함으로써 다양한 이미지 포맷과 해상도에 대한 테스트를 손쉽게 확장한다. 테스트 벡터는 레퍼런스 모델의 입력/출력 트랜잭션을 캡처하고, 자동으로 시뮬레이션 스크립트와 체크러를 생성하도록 설계되어, 검증 엔지니어가 수작업으로 벡터를 작성하는 부담을 크게 줄인다.

재사용 측면에서는, 동일한 TLM 레퍼런스 모델을 여러 프로젝트에서 공유하거나, 비이미지 신호 처리(IP)에도 동일한 흐름을 적용할 수 있다. 이는 검증 인프라 구축 비용을 절감하고, 팀 간 지식 이전을 촉진한다. 또한, 초기 검증 단계에서 발견된 설계 결함은 RTL 구현 단계에서 수정하기보다 레퍼런스 모델 수준에서 빠르게 수정할 수 있어, 전체 설계 주기의 리스크를 낮춘다.

마지막으로, 본 접근법은 시뮬레이션 속도와 정확도 사이의 트레이드오프를 고려한다. TLM 모델은 RTL에 비해 훨씬 빠른 실행 시간을 제공하지만, 사이클 정확도는 낮다. 따라서, 주요 기능 검증과 초기 커버리지 확보에는 충분히 유효하지만, 최종 타이밍 검증이나 전력 분석 등 정밀 검증은 RTL 기반 시뮬레이션으로 전환해야 한다는 점을 명시한다. 이러한 단계적 검증 흐름은 프로젝트 일정에 맞춰 검증 리소스를 효율적으로 배분할 수 있게 한다.