뇌형 연관 학습을 구현한 나노상변화 메모리 시냅스 배열

초록

본 논문은 상변화 메모리(PCM) 셀을 시냅스로 사용하여 2차원 배열 형태의 신경망을 실험적으로 구현하고, Hebbian 학습 규칙을 적용해 연관 기억(패턴 저장·복원)을 수행한다. 장치 저항 변동성을 학습 에폭 수 증가로 보정할 수 있음을 확인했으며, 변동성 허용 범위와 전체 에너지 소비 사이의 트레이드오프를 정량적으로 분석하였다.

상세 분석

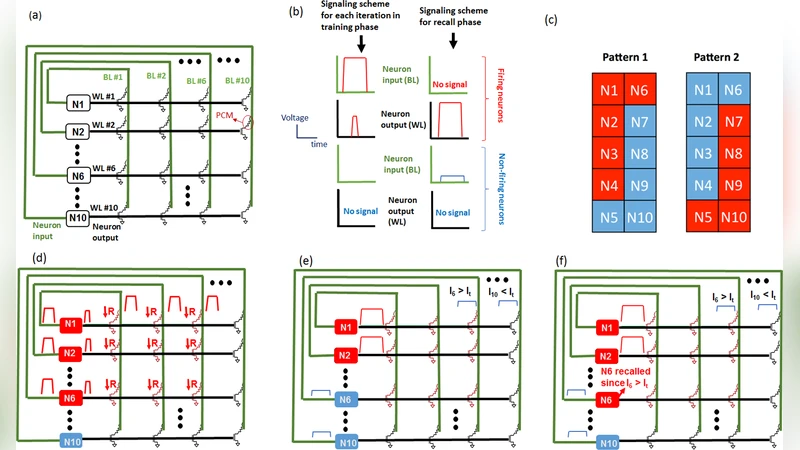

이 연구는 두 가지 핵심 기술을 결합한다. 첫째, 상변화 메모리(PCM) 소자를 시냅스 역할로 활용한다는 점이다. PCM은 비휘발성 저항 변화를 제공하며, 전류 펄스를 통해 amorphous와 crystalline 상태 사이의 중간 저항값을 연속적으로 조절할 수 있다. 이러한 아날로그 저항 조정은 시냅스 가중치의 가변성을 구현하는 데 적합하다. 둘째, 다수의 PCM 셀을 격자(grid) 형태로 배열하고, 각 교차점에 전압 라인을 배치해 신경망의 연결 구조를 물리적으로 구현한다. 이는 생물학적 뇌의 뉴런-시냅스 네트워크와 유사한 토폴로지를 제공한다는 점에서 의미가 크다.

학습 메커니즘은 전통적인 Hebbian 원칙, 즉 “함께 발화하는 뉴런은 연결이 강화된다”를 전기적 펄스로 구현한다. 입력 패턴을 전압 라인에 인가하면, 활성화된 행과 열이 교차하는 PCM 셀에 프로그래밍 펄스가 가해져 저항이 감소(가중치 강화)한다. 반대로 비활성 교차점은 변화가 거의 없으며, 이는 억제 연결을 자연스럽게 형성한다. 실험에서는 4×4, 8×8 등 다양한 규모의 배열을 사용했으며, 각 배열에 대해 2~3개의 이진 패턴을 학습시킨 뒤, 일부 입력을 제거한 상태에서 연관 복원을 테스트하였다. 결과는 기대한 대로 누락된 입력이 있더라도 전체 패턴이 정확히 재구성되는 것을 보여준다.

변동성에 대한 분석은 두 가지 측면에서 이루어졌다. 첫째, 개별 PCM 셀의 초기 저항 분포가 넓어도 학습 에폭을 늘리면 평균 가중치가 수렴하여 전체 네트워크 성능이 유지된다. 이는 학습 과정이 통계적 평균화 역할을 하여 장치 간 불균형을 보정한다는 의미다. 둘째, 변동성 허용 한계를 정량화하기 위해, 저항 변동 폭을 10 %에서 50 %까지 인위적으로 확대한 뒤 학습 성공률을 측정했다. 변동이 클수록 더 많은 에폭이 필요했으며, 그에 따라 전체 에너지 소비가 증가했다. 따라서 변동성 허용 범위와 에너지 효율 사이에 명확한 트레이드오프가 존재함을 확인하였다.

에너지 분석에서는 프로그래밍 펄스의 전압·시간 파라미터와 배열 규모를 고려한 총 전력 소모를 계산했다. 변동성이 낮은 경우, 적은 에폭으로 목표 저항값에 도달하므로 에너지 효율이 크게 향상된다. 반면 변동성을 크게 허용하면 학습 단계가 늘어나면서 누적 에너지 소비가 수 배 증가한다. 이러한 결과는 실제 하드웨어 구현 시, 장치 공정의 품질 관리와 학습 알고리즘 설계가 상호 보완적으로 최적화되어야 함을 시사한다.

전반적으로 이 논문은 단일 PCM 소자 수준을 넘어, 실제 물리적 배열에서 연관 기억을 구현한 최초 사례 중 하나이며, 변동성 관리와 에너지 효율성에 대한 실험적 데이터를 제공한다. 이는 차세대 뉴로모픽 시스템 설계에 있어 비휘발성 아날로그 메모리의 실용성을 크게 높이는 중요한 진전으로 평가될 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기