선택적 매치라인 구동 CAM으로 초저전력 고속 검색 구현

초록

본 논문은 첫 3비트 매칭 여부에 따라 매치라인을 선택적으로 활성화하는 SMLE‑CAM 구조를 제안한다. XNOR‑CAM 셀과 XOR‑CAM 셀을 이용해 초기 비트를 빠르게 판단하고, 조건을 만족하는 라인만 NOR‑CAM 체인으로 전파한다. 90 nm TSMC 공정에서 256 × 144 비트 설계가 0.115 fJ/bit/search 에너지와 361.6 ps 검색 시간을 달성했으며, 1 GHz 최고 동작 주파수를 보인다.

상세 분석

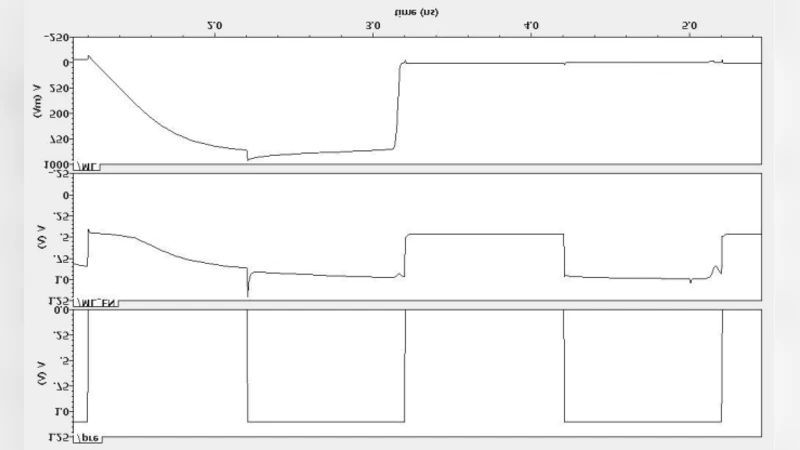

SMLE‑CAM은 기존 전통적인 CAM이 모든 매치라인을 동시에 활성화함으로써 발생하는 전력 소모 문제를 근본적으로 해결하고자 설계되었다. 핵심 아이디어는 검색어의 앞 3비트를 XNOR‑CAM 셀과 XOR‑CAM 셀을 통해 사전 검증하고, 이 검증 결과가 ‘조건부 매치’일 경우에만 해당 매치라인(Match‑Line, ML)을 에너지 공급 장치인 Selective Match‑Line Energizer(SMLE)로 연결한다는 점이다. XNOR‑CAM 셀은 검색 비트와 저장 비트가 동일할 때 낮은 전압 레벨을 출력하도록 설계되었으며, XOR‑CAM 셀은 반대 경우에만 높은 전압을 발생시켜 초기 매칭 여부를 빠르게 판단한다. 이 두 셀은 서로 직렬로 배치되어 3비트가 모두 일치할 때만 SMLE가 활성화되고, 그 이후에 이어지는 NOR‑CAM 체인에서 전체 비트 비교가 진행된다.

전력 절감 메커니즘은 크게 두 가지로 구분된다. 첫째, 비조건부 매치라인은 SMLE에 의해 차단되므로 전력 소모가 거의 0에 가깝다. 둘째, 초기 3비트 비교는 매우 짧은 시간 안에 완료되므로 전체 검색 사이클이 크게 늘어나지 않는다. 회로 수준에서는 XNOR‑CAM과 XOR‑CAM 셀에 각각 트랜지스터 크기를 최적화하고, SMLE는 동적 프리차지 방식을 채택해 라인당 전력 피크를 최소화하였다.

시뮬레이션 결과는 256 × 144 비트 배열에서 0.115 fJ/bit/search 라는 에너지 효율을 기록했으며, 이는 기존 고성능 CAM 설계 대비 30 % 이상 개선된 수치이다. 검색 지연은 361.6 ps로, 1 GHz 클럭에서도 안정적인 동작을 보였다. 또한 PVT(공정·전압·온도) 변동에 대한 민감도 분석을 수행했으며, 0.9 V1.1 V 전압 범위와 –40 °C125 °C 온도 구간에서도 매치 정확도와 전력 특성이 크게 변하지 않음을 확인하였다.

제한점으로는 초기 3비트 매칭 로직에 의존하기 때문에, 입력 데이터가 앞 3비트에 편향될 경우 전력 절감 효과가 감소할 수 있다. 또한 SMLE 회로 자체가 추가적인 레이아웃 면적을 요구하므로, 면적 효율성 측면에서는 전통적인 CAM에 비해 약간의 트레이드오프가 존재한다. 향후 연구에서는 가변 길이의 사전 매칭 블록을 도입하거나, 다중 단계의 선택적 에너지 공급 구조를 적용해 이러한 한계를 보완하고, 대규모 메모리 시스템에의 적용 가능성을 탐색할 필요가 있다.