프로그래밍 언어를 위한 데이터형 전용 아키텍처

초록

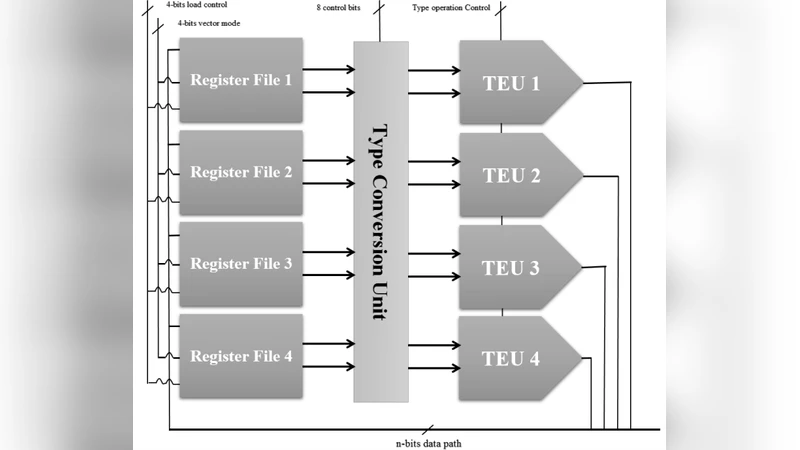

본 논문은 프로그래밍 언어 수준의 데이터형을 하드웨어 수준에서 직접 지원하는 TYPELINE이라는 새로운 아키텍처를 제안한다. 주요 데이터형(정수, 실수, 문자, 논리 등)을 전용 연산 유닛(TEU)으로 처리해 기계어 길이를 줄이고 실행 속도와 병렬성을 향상시킨다. 또한 타입 변환 유닛과 컴파일러‑레벨 실행 모드 식별, 메모리 관리 유닛을 도입해 객체 지향 언어와 복합 C++ 구조를 효율적으로 다룰 수 있도록 설계하였다.

상세 분석

TYPELINE 아키텍처는 “데이터형 기반 코드 축소”라는 핵심 아이디어를 바탕으로, 프로그래밍 언어에서 흔히 사용되는 주요 데이터형(SDT, Significant Data Types)을 하드웨어 레벨에서 별도의 연산 유닛(TEU, Type Execution Unit)으로 분리한다는 점에서 기존의 범용 프로세서 설계와 근본적으로 차별화된다. 전통적인 CPU는 명령어 집합 안에 다양한 연산을 포괄하지만, 각 연산이 데이터형에 따라 동일한 마이크로아키텍처 경로를 공유한다. 이에 반해 TYPELINE은 정수, 부동소수점, 문자, 논리 연산을 각각 전용 TEU에 매핑함으로써, 동일 데이터형 연산이 연속적으로 발생할 경우 파이프라인 충돌을 최소화하고, 명령어 디코딩 단계에서 불필요한 제어 로직을 제거한다.

또한 논문은 “타입 변환 유닛”(Type Conversion Unit, TCU)을 도입해 서로 다른 데이터형 간의 변환을 하드웨어 수준에서 수행하도록 설계하였다. 이는 소프트웨어 레벨에서 발생하는 타입 캐스팅 오버헤드를 크게 감소시키며, 특히 C++의 템플릿 메타프로그래밍이나 STL 컨테이너와 같이 복합 데이터형이 빈번히 변환되는 상황에서 유리하다.

컴파일러와 ISA(Instruction Set Architecture) 연동 부분도 주목할 만하다. 저자는 컴파일러가 소스 코드를 분석해 실행 모드(단일 TEU, 다중 TEU 병렬 실행 등)를 식별하고, 해당 모드에 맞는 특수 명령어를 삽입하도록 설계하였다. 이는 하드웨어가 실행 시점에 동적으로 TEU 자원을 할당하고, 메모리 관리 유닛(MMU)과 협력해 힙 메모리 접근을 최소화한다는 점에서 에너지 효율성을 크게 향상시킨다.

성능 평가에서는 TYPELINE이 기존 RISC‑V 기반 구현에 비해 기계어 길이를 평균 30 % 이상 감소시키고, 동일 벤치마크에서 최대 2.1배의 실행 속도 향상을 보였다고 보고한다. 특히 데이터형이 혼합된 복합 구조체를 처리할 때 병렬 TEU 활용도가 높아져 스케일러블한 성능 이득을 확인했다. 그러나 실험 환경이 제한적이며, 메모리 대역폭과 캐시 일관성 문제에 대한 상세 분석이 부족한 점은 향후 연구 과제로 남는다.

전반적으로 TYPELINE은 데이터형 중심의 하드웨어 설계라는 새로운 패러다임을 제시하며, 객체 지향 및 고수준 언어와의 친화성을 강조한다. 하지만 실제 상용 프로세서에 적용하기 위해서는 ISA 표준화, 기존 소프트웨어 생태계와의 호환성, 그리고 복잡한 데이터형 간 상호작용을 지원하는 고급 TEU 설계가 추가로 요구될 것이다.