고속 저전력 AMP 기반 오디오 복원 VLSI 설계

초록

본 논문은 Approximate Message Passing(AMP) 알고리즘을 활용한 오디오 신호 복원을 위해 전용 VLSI 구조인 AMP‑M을 제안한다. 고정비 16‑bit Wallace 트리 멀티플라이어, FFT‑MUX, 다중 RAM 모듈을 결합해 연산량을 최소화하고, Early Termination 기법으로 반복 횟수를 줄여 실시간 처리에 적합한 고처리량(≈408 MHz)·저전력(≈65 mW)·소형 면적(≈24 % 논리소자 사용)을 구현하였다.

상세 분석

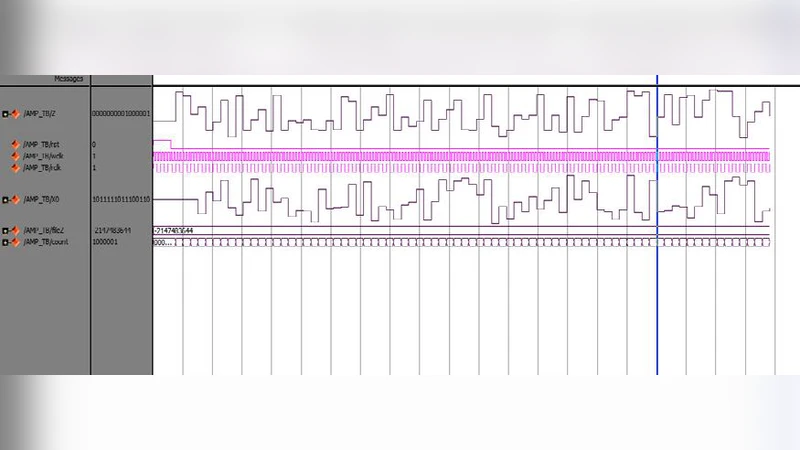

이 논문은 압축 센싱 기반 오디오 복원 문제를 해결하기 위해 AMP 알고리즘의 빠른 수렴 특성과 낮은 연산 복잡도를 하드웨어 수준에서 구현하려는 시도를 상세히 기술한다. 제안된 AMP‑M 아키텍처는 크게 네 가지 핵심 블록으로 구성된다. 첫째, 16‑bit 고정비 Wallace 트리 멀티플라이어를 채택한 MAC 유닛은 곱셈·누산 연산을 파이프라인화함으로써 연산 지연을 최소화하고, 면적·전력 효율을 크게 향상시킨다. 둘째, FFT‑MUX 모듈은 입력 잔차(z) 값을 DCT/IDCT 기반의 M/2 길이 FFT/IFT 연산으로 변환하여 스파스 표현을 강화한다. 이 과정에서 재배열·축소·트윌드 팩터 회전 등을 수행해 주파수 도메인에서의 잡음 억제를 가능하게 한다. 셋째, Z‑RAM·X‑RAM·RMSE‑TR‑SH‑L0‑UNIT 등 전용 메모리 블록은 잔차, 추정 신호, RMS‑Error 등을 실시간으로 저장·읽어들이며, Early Termination(ET) 로직을 통해 RMS‑Error가 사전 정의 임계값 이하가 되면 반복을 즉시 종료한다. 이는 평균 28회 이하의 반복으로도 충분히 수렴함을 실험적으로 확인하였다. 넷째, 전체 설계는 Altera Quartus II 기반 Cyclone III DE0 보드에 구현되어 15 408개의 논리 소자 중 3 693개(≈24 %)만 사용하면서 408.5 MHz의 클럭 주파수와 65.43 mW의 전력 소모를 달성한다. 논문은 또한 기존 IP8M 65 nm CMOS 구현과 비교해 전력·처리량 모두 우수함을 표로 제시한다. 다만, 설계가 16‑bit 고정소수점에 국한되어 있어 매우 높은 다이내믹 레인지가 요구되는 오디오(예: 24‑bit/96 kHz)에는 추가적인 정밀도 확장이 필요할 것으로 보인다. 또한, FFT‑MUX가 DCT 기반 전처리를 전제로 하므로 비정형 측정 행렬(A)이 존재할 경우 성능 저하 가능성이 있다. 전반적으로 AMP‑M은 스파스 복원 알고리즘을 VLSI 수준에서 효율적으로 구현한 사례로, 실시간 의료 영상(MRI), 레이더, 무선 통신 등 다양한 분야에 적용 가능성을 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기