맞춤형 하드웨어 확장을 위한 YARDstick 자동화 도구

초록

YARDstick은 애플리케이션 특화 명령어와 하드웨어 확장을 자동으로 생성·평가하는 설계 자동화 프레임워크이다. 사용자 정의 중간 표현(IR)을 기반으로 어플리케이션 분석, 커스텀 인스트럭션(CI) 탐색, 선택, 그리고 하드웨어 추정까지 일관된 흐름을 제공한다. 기존 ASIP 설계에서 발생하는 컴파일러·시뮬레이터 종속성 문제를 해소하고, 다양한 타깃 아키텍처와 메모리 모델을 자유롭게 실험할 수 있다.

상세 분석

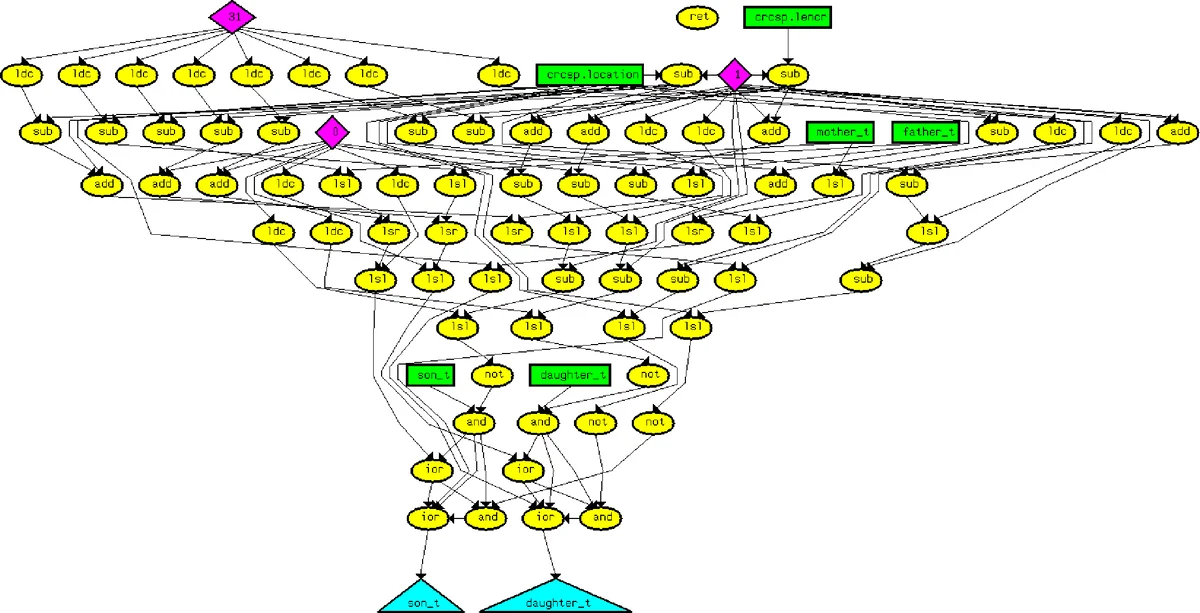

YARDstick은 세 개의 핵심 라이브러리(libByoX, libPatCUTE, libmachine)와 BXIR이라는 타깃 아키텍처 기술 파일로 구성된다. libByoX는 ISeq와 CFG 같은 내부 데이터 구조를 파싱하고, 사용자 정의 IR을 자유롭게 조작할 수 있는 API를 제공한다. 이를 통해 어플리케이션의 데이터 의존성 그래프와 제어 흐름을 정확히 캡처하고, 레지스터 라이프타임·루프 구조 등 정적·동적 메트릭을 수집한다. libPatCUTE는 패턴 기반 CI 생성·선택 엔진으로, MAXMISO, 제한된 MISO, 그리고 휴리스틱 기반 MIMO 탐색 알고리즘을 포함한다. 특히 MIMO 탐색에서는 서브그래프가 패턴보다 성능 이득이 낮다는 가정을 이용해 선형 시간에 근사해를 얻으며, 필요 시 지수 복잡도 알고리즘으로 전환할 수 있다. 선택 단계에서는 사이클 이득, 면적 대비 이득 등 다중 목표 함수를 지원하는 그리디와 0‑1 배낭 방식이 제공된다. libmachine은 타깃 아키텍처에 대한 구체적 비용(면적·지연·사이클) 정보를 BXIR 형식으로 정의하도록 요구한다; 따라서 새로운 ISA를 추가하려면 libmachine만 재타깃팅하면 된다.

YARDstick의 API는 기본 블록 수준에서 입력·출력·상수 오퍼랜드를 자동으로 식별하고, SSA‑형식으로 통합해 중복 패턴을 제거한다. CI 생성 흐름은 ‘init_opnd_library’ → ‘find_input_opnds’ 등 일련의 함수 호출로 구성되며, 사용자는 MISO·MIMO 중 원하는 탐색 방법을 선택한다. 생성된 CI는 ISeq 형태로 저장되어 기존 CFG·BB와 동일한 파이프라인을 통해 시뮬레이션, VHDL 변환, 그래프 시각화 등 다양한 백엔드로 내보낼 수 있다.

실험에서는 세 가지 IR(확장된 SUIFvm, 제한 레지스터 집합을 가진 SUIF rmenh, iDLX)과 여러 벤치마크(CRC, IDEA, SHA, ADPCM, FIR, Motion‑Estimation)를 사용해 CI 생성 효율을 평가하였다. 결과는 IR에 비트 조작 연산이 포함될 경우 MIMO 패턴이 크게 늘어나고, 레지스터 수가 제한된 경우 MAXMISO가 더 실용적임을 보여준다. 또한 메모리 모델(로드/스토어 비용)과 입력/출력 제약을 바꾸면 최적 CI 집합이 급격히 변함을 확인했다.

YARDstick은 기존 연구(Pattlib, Xtensa, VLIW 기반 CI 생성 등)와 달리 컴파일러·시뮬레이터에 종속되지 않는 독립적인 탐색 인프라를 제공한다. IR을 자유롭게 정의하고, 커스텀 분석·최적화를 플러그인 형태로 삽입할 수 있어, 설계자에게 높은 유연성을 부여한다. 다만 현재는 BXIR 기반 비용 모델링과 백엔드 연결이 수작업으로 이루어져 자동화 수준이 제한적이며, 대규모 애플리케이션에 대한 스케일링 테스트가 부족한 점이 아쉽다.

댓글 및 학술 토론

Loading comments...

의견 남기기