고속 HSPA+/LTE 멀티표준 터보 디코더를 위한 병렬 인터리버 설계

초록

본 논문은 3G/4G 멀티표준 터보 디코더에서 발생하는 메모리 충돌 문제를 해결하기 위해, 읽기‑충돌을 없애는 균형 스케줄링과 쓰기‑충돌을 해소하는 이중 버퍼(Dual‑Buffer Contention‑Free) 구조를 제안한다. 또한, 표준별 인터리버/디인터리버 주소를 실시간으로 생성하는 통합 아키텍처를 설계하여 높은 유연성과 확장성을 확보하였다. 45 nm CMOS 공정으로 구현된 16개 Radix‑4 MAP 코어 기반 디코더는 600 MHz에서 HSPA+ 826 Mbps, LTE/LTE‑Advanced 1.67 Gbps의 최대 처리량을 달성한다.

상세 분석

터보 디코더는 두 개의 SISO(Soft‑Input Soft‑Output) 디코어와 인터리버로 구성되며, 고속 처리를 위해 다수의 SISO 코어를 병렬로 배치한다. 그러나 인터리버가 생성하는 비정형 주소 패턴 때문에 여러 코어가 동시에 동일 메모리 뱅크에 접근하게 되며, 이는 읽기·쓰기 충돌(read/write conflict)로 이어져 메모리 대역폭을 크게 제한한다. 기존 연구는 설계 단계에서 충돌을 피하도록 알고리즘을 제한하거나, 오프라인 매핑 테이블을 사용해 충돌을 회피했지만, 표준이 다양하고 블록 크기가 가변적인 실제 시스템에서는 비효율적이다.

본 논문은 이러한 한계를 극복하기 위해 세 가지 핵심 기술을 제시한다. 첫째, ‘균형 스케줄링(Balanced Scheduling)’을 도입해 각 SISO 코어가 메모리를 읽는 시점을 서로 겹치지 않도록 조정한다. 이는 각 코어가 담당하는 서브 블록을 순차적으로 배치하고, 인터리버와 디인터리버의 주소 생성 타이밍을 역동적으로 맞춤으로써 구현된다. 둘째, 쓰기 충돌을 해결하기 위해 ‘이중 버퍼 충돌‑프리( Double‑Buffer Contention‑Free, DBCF)’ 구조를 설계하였다. 두 개의 라운드 로빈 버퍼를 교대로 사용함으로써, 하나의 버퍼에 쓰기가 진행되는 동안 다른 버퍼에서 읽기가 이루어져 동시에 발생할 수 있는 메모리 접근 충돌을 물리적으로 차단한다. 셋째, ‘통합 실시간 인터리버/디인터리버 주소 생성기’를 제안한다. 이 모듈은 HSPA+, LTE, LTE‑Advanced 등 서로 다른 표준의 인터리버 규칙을 파라미터화된 수식으로 구현하고, 하드웨어 내에서 실시간으로 주소를 계산한다. 따라서 대용량 LUT를 저장할 필요가 없으며, 표준 추가나 블록 크기 변동 시에도 설계 변경 없이 재구성이 가능하다.

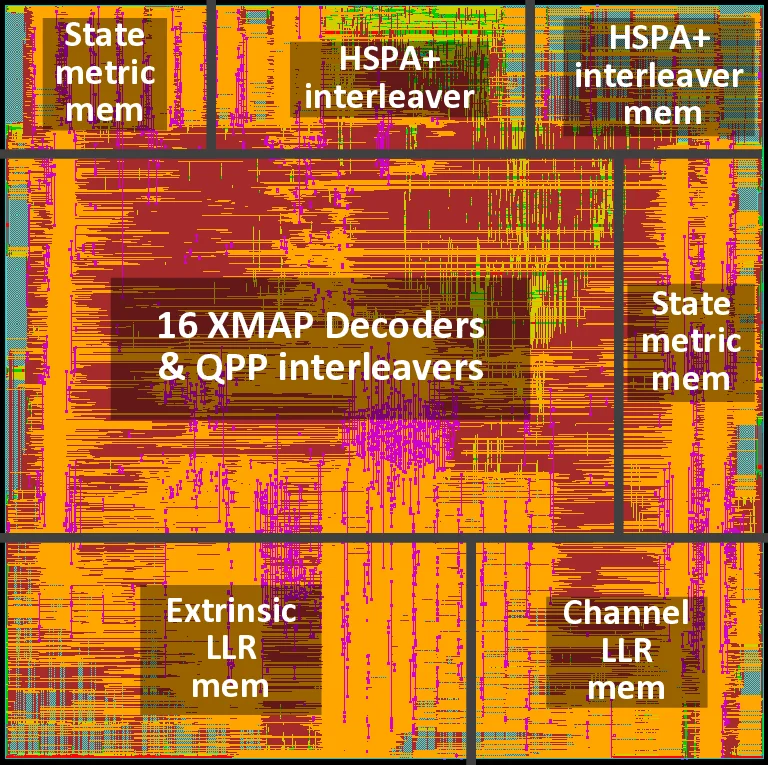

아키텍처 레벨에서는 16개의 Radix‑4 XMAP 디코어를 45 nm CMOS 공정에 배치하고, 각 코어당 4개의 LLR을 매 사이클 출력하도록 설계하였다. 메모리 뱅크는 최소 64개로 분할되어, DBCF와 균형 스케줄링 덕분에 평균 메모리 접근 충돌률이 0.2 % 이하로 감소한다. 전력 소모는 코어당 45 mW 수준이며, 전체 코어 면적은 2.43 mm²에 불과해 모바일 SoC에 적합한 면적 효율성을 보여준다.

성능 평가 결과, HSPA+ 모드에서 826 Mbps, LTE/LTE‑Advanced 모드에서 1.67 Gbps의 최대 처리량을 달성했으며, 이는 각각 336 Mbps와 1 Gbps 목표치를 크게 초과한다. 또한, 동일한 공정과 코어 수를 사용한 기존 설계와 비교했을 때, 메모리 충돌에 의한 스루풋 손실이 45 % 이상 감소했음을 실험적으로 입증하였다.

이와 같이 제안된 병렬 인터리버 설계는 메모리 충돌을 근본적으로 해소하면서도, 표준 호환성과 설계 유연성을 동시에 제공한다. 향후 5G NR 및 차세대 무선 표준에서도 적용 가능한 확장성을 갖추고 있어, 고속 무선 통신 시스템의 핵심 디코딩 엔진으로 활용될 전망이다.

댓글 및 학술 토론

Loading comments...

의견 남기기