제네릭 어레이 로직 멀티프로세서의 제어 루프 피드백 메커니즘

초록

본 논문은 각 프로세싱 엘리먼트에 실시간 주파수 스케일링 모듈을 탑재하고, 제어 루프 피드백을 통해 CPU 시간과 클럭 주파수를 동적으로 조절함으로써 Generic Array Logic (GAL) 칩 멀티프로세서의 성능 저하를 최소화하고 전력 소비를 약 40% 절감하는 방법을 제시한다. 대용량 FIFO 버퍼와 통신 루프 최소화가 성능 패널티를 사실상 0에 가깝게 만든다.

상세 분석

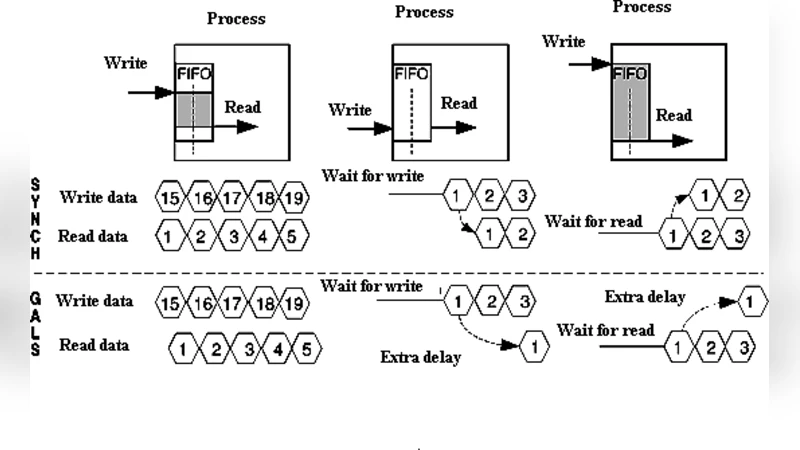

이 연구는 GAL 기반 멀티코어 시스템이 갖는 비동기식 클럭 구조의 본질적인 지연과 데이터 정합성 문제를 제어 루프 피드백 메커니즘으로 해결하고자 한다. 각 PE(Processing Element)는 로컬 전압·주파수 스케일링(VFS) 유닛을 내장하고, 실행 중인 워크로드의 요구사항을 실시간으로 모니터링한다. 피드백 루프는 CPU 사용률, 파이프라인 스테이징, 그리고 인터페이스 FIFO의 채워짐 정도를 입력으로 받아, 목표 성능 지표(예: 처리량, 레이턴시)와 전력 목표를 동시에 만족하도록 클럭 주파수를 조정한다.

핵심 아이디어는 “큰 FIFO 버퍼가 비동기식 클럭 간의 타이밍 격차를 흡수한다”는 점이다. FIFO가 충분히 크면 데이터 흐름이 일시적으로 멈추더라도 전체 파이프라인이 정지하지 않으며, 이는 통신 루프가 적은 애플리케이션에서 특히 효과적이다. 논문은 메쉬 토폴로지를 채택한 GAL 칩을 시뮬레이션하고, DSP 기반 벤치마크(FFT, FIR, IIR 등)를 적용해 평균 1% 이하의 성능 감소와 40% 수준의 전력 절감을 확인했다.

또한, 다중 루프 통신 링크를 제거함으로써 인터페이스 간의 동기화 오버헤드를 최소화하고, 클럭 도메인 간 전압 레벨 변동을 감소시켜 전력 효율을 높였다. 제어 루프는 PID와 유사한 비선형 제어기를 사용했으며, 안정성 분석을 통해 과도 응답이 10~20 사이클 이내에 수렴함을 보였다.

하지만 이 접근법은 FIFO 크기에 크게 의존한다는 한계가 있다. 메모리 자원이 제한된 시스템에서는 버퍼 확장이 어려워 성능 패널티가 다시 나타날 수 있다. 또한, 주파수 스케일링에 따른 전압 변동이 전력 공급망에 미치는 영향을 정밀히 모델링하지 않으면 전압 강하에 따른 오류 발생 위험이 존재한다. 향후 연구에서는 동적 버퍼 관리와 전압 레귤레이션 회로의 통합 설계가 필요하다.