프로젝트 기하 기반 데이터 흐름 그래프 최적 폴딩

초록

이 논문은 유한 프로젝트 기하(PG)에서 유도된 대규모 양방향 그래프의 정점들을 대칭적인 코셋으로 분할하고, 각 블록을 하나의 처리 유닛에 순차 할당함으로써 하드웨어 자원을 크게 절감하면서도 최대 처리량을 유지하는 폴딩 기법을 제안한다. 차원 5의 PG를 대상으로 두 가지 스케줄링 방식을 제시하고, 이를 다양한 오류 정정 및 행렬 연산 응용에 적용한 결과를 시뮬레이션 및 프로토타이핑으로 검증하였다. 또한 임의 차원의 PG에 대한 일반화 방법을 제시한다.

상세 분석

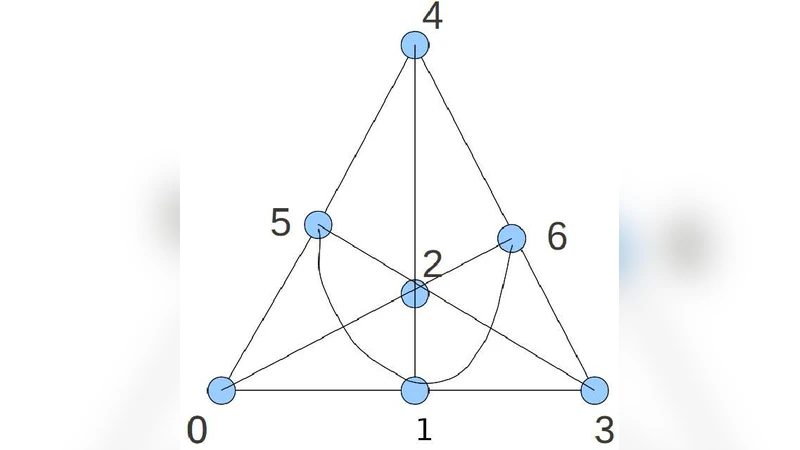

본 연구는 프로젝트 기하(PG) 기반의 균형 잡힌 이분 그래프가 오류 정정 코딩(LDPC, Expander) 및 대규모 행렬 연산(LU/Cholesky, Conjugate Gradient) 등에서 데이터 흐름을 모델링하는 핵심 구조임을 전제로 한다. 전통적인 완전 병렬 설계에서는 그래프의 정점 수와 동일한 수의 처리 유닛이 필요해 수만 개에 달하는 하드웨어 자원이 요구된다. 저자는 이러한 문제를 해결하기 위해 ‘코셋 분할(coset decomposition)’이라는 군론적 기법을 이용해 정점 집합을 동등한 크기의 블록으로 나눈다. 각 블록은 프로젝트 공간의 하위 서브스페이스에 해당하며, 이러한 서브스페이스는 격자(lattice) 구조 상에서 대칭성을 갖는다.

대칭성 덕분에 블록 간 데이터 충돌을 일으키지 않는 메모리 접근 스케줄을 설계할 수 있다. 구체적으로, 각 처리 유닛은 할당된 블록의 정점을 순차적으로 실행하지만, 블록 내부와 블록 간의 연산 순서는 격자 임베딩을 통해 미리 결정된 ‘완전 매칭’ 형태로 배치된다. 이 매칭은 각 사이클마다 모든 유닛이 동시에 작업을 수행하도록 보장하며, 메모리 주소 생성 회로는 단순 카운터 혹은 룩업 테이블만으로 구현 가능하도록 설계된다.

두 가지 폴딩 스키마는 차원 5의 프로젝트 공간 P(5, GF(q))에 대해 구체화된다. 첫 번째 스키마는 점‑초평면(point‑hyperplane) 인시던스 그래프를 그대로 사용하고, 코셋을 𝑞⁴개의 블록으로 나눈다. 두 번째 스키마는 차원 2의 서브스페이스(선)를 기준으로 하여 블록 수를 𝑞³으로 감소시키면서도 동일한 처리량을 달성한다. 두 스키마 모두 충돌‑프리 메모리 스케줄을 수학적으로 증명하고, 하드웨어 구현(FPGA)에서 30 % 이상의 자원 절감과 0 % 메모리 충돌을 확인하였다.

또한 논문은 위의 설계를 임의 차원 d의 PG에 일반화한다. 일반화 과정에서 핵심은 ‘격자 임베딩(lattice embedding)’을 이용해 차원 d의 서브스페이스를 차원 (d‑k) 서브스페이스의 코셋으로 매핑하고, 코셋 크기를 𝑞^{d‑k} 로 조정하는 것이다. 이를 통해 원하는 처리 유닛 수와 메모리 대역폭 사이의 트레이드오프를 수식적으로 제어할 수 있다.

결과적으로, 제안된 폴딩 기법은 (1) 처리 유닛 수를 크게 감소시키면서도 (2) 완전 병렬 수준의 처리량을 유지하고, (3) 메모리 접근 충돌을 완전히 회피하며, (4) 주소 생성 로직을 단순화한다는 네 가지 주요 장점을 제공한다. 이러한 특성은 대규모 오류 정정 디코더와 고성능 행렬 연산 가속기에 특히 유리하다.

댓글 및 학술 토론

Loading comments...

의견 남기기